# MODEL: NDM3Z-90 | DESCRIPTION: AUTO COMPENSATED, DIGITAL DC-DC POL CONVERTER

#### **GENERAL CHARACTERISTICS**

- 7.5~14 V input range

- 0.6~1.8 V programmable output

- high efficiency

- voltage tracking

- voltage margining

- active current sharing

- Snapshot<sup>™</sup> parametric capture

- voltage/current/temperature monitoring

- synchronization and phase spreading

- remote differential voltage sense

- programmable soft start and soft stop

- fault management

#### FEATURES

- compact package vertical:

50.8 x 9.51 x 19.05 mm (2.0 x 0.37 x 0.75 in) horizontal:

50.8 x 19.05 x 10.0 mm

- (2.0 x 0.75 x 0.39 in)

- 90 A output

- adaptive algorithms

- cycle-by-cycle charge management

- dual phase architecture

- SMBus interface

- PMBus<sup>™</sup> compatible

| MODEL    | input voltage | output voltage | output current | output wattage |

|----------|---------------|----------------|----------------|----------------|

|          | (Vdc)         | (Vdc)          | max<br>(A)     | max<br>(W)     |

| NDM3Z-90 | 7.5~14        | 0.6~1.8        | 90             | 162            |

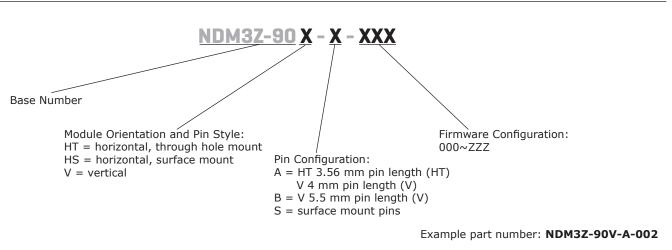

## PART NUMBER KEY

$\ast$  HS and HT modules are delivered on tape and reel

.....

\* V modules are delivered in trays

## **CONTENTS**

| Pin Descriptions2                  |

|------------------------------------|

| Absolute Maximum Ratings4          |

| Product Electrical Specifications4 |

| Mechanical Drawings   | 14~15 |

|-----------------------|-------|

| PMBus Interface       | 17    |

| Operating Information | 20    |

vertical module

4.0 mm pin length firmware configuration 002

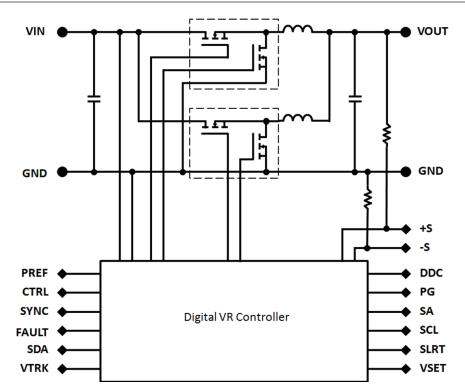

# **INTERNAL CIRCUIT DIAGRAM**

### **POWER CONNECTIONS**

| symbol | pin            | IO type | description          |

|--------|----------------|---------|----------------------|

| VIN    | 1A, 1B, 1C, 1D | Power   | Input voltage        |

| GND    | 2A, 2B, 2C, 2D | Ground  | Power ground         |

| VOUT   | 3A, 3B, 3C, 3D | Power   | Output voltage       |

| N/C    | 11, 12         | N/A     | No connect on module |

# **COMMUNICATION CONNECTIONS**

| symbol | pin | IO type | description                                                                                                 |

|--------|-----|---------|-------------------------------------------------------------------------------------------------------------|

| +S     | 4A  | Analog  | Output voltage positive sense input, N/C if not used                                                        |

| -S     | 4B  | Analog  | Output voltage negative sense input, N/C if not used                                                        |

| VSET   | 5A  | Digital | Output voltage pin-strap                                                                                    |

| VTRK   | 5B  | Analog  | Voltage tracking input, N/C if not used                                                                     |

| SLRT   | 6A  | Digital | SMBus alert, N/C if not used                                                                                |

| SDA    | 6B  | Digital | SMBus data, pull-up resistor required even if not used                                                      |

| SCL    | 7A  | Digital | SMBus clock, pull-up resistor required even if not used                                                     |

| FAULT  | 7B  | Digital | Module fault indicator, N/C if module is stand-alone, tied together if modules are current share configured |

| SA     | 8A  | Digital | SMBus address pinstrap                                                                                      |

| SYNC   | 8B  | Digital | Synchronization I/O, N/C if not used                                                                        |

| PG     | 9A  | Digital | Power good, pull-up resistor or configured as push-pull                                                     |

| CTRL   | 9B  | Digital | Remote control or enable, N/C if not used, internal pull-up resistor                                        |

| DDC    | 10A | Digital | Digital-DC Communications bus, pull-up resistor or<br>configured as push-pull (stand-alone only) required   |

| PREF   | 10B | Ground  | Pin-strap ground                                                                                            |

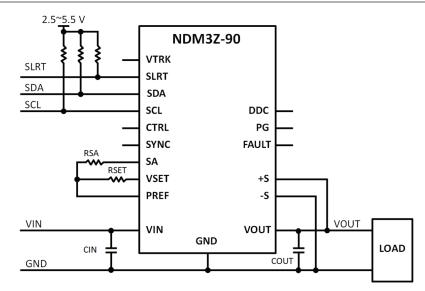

### **TYPICAL APPLICATION CIRCUIT**

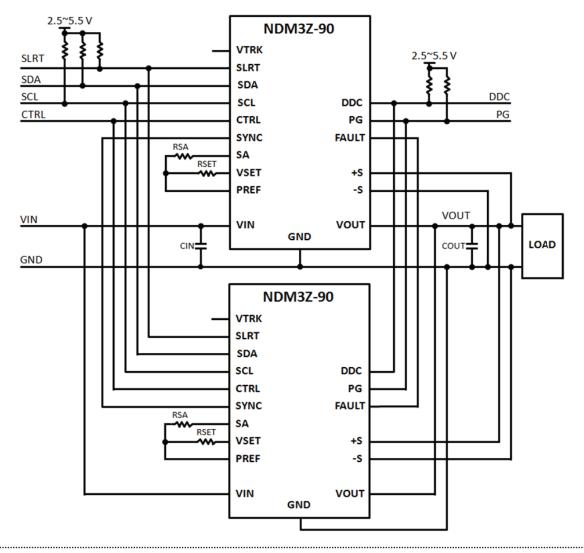

# **TYPICAL APPLICATION CIRCUIT - PARALLEL OPERATION**

### **ABSOLUTE MAXIMUM RATINGS**

| parameter                   | conditions/description                                  | min  | typ | max | units |

|-----------------------------|---------------------------------------------------------|------|-----|-----|-------|

| V <sub>in</sub>             | input voltage                                           | -0.3 |     | 16  | V     |

| digital pin voltage         | CTRL, DDC, SA, SLRT, SDA, SCL, SYNC, VSET, PG,<br>FAULT | -0.3 |     | 6.0 | V     |

| analog pin voltage          | +S, V <sub>o</sub> , VTRK                               | -0.3 |     | 6.5 | V     |

| ground voltage differential | GND, PREF, -S                                           | -0.3 |     | 0.3 | V     |

| operating temperature       | T <sub>P1</sub>                                         | -40  |     | 150 | °C    |

| storage temperature         |                                                         | -40  |     | 150 | °C    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for Notes: extended periods may affect device reliability. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the Electrical Specification section of this specification is not implied.

### **Configuration File**

The digital control circuit in this module uses a configuration file which determines the functionality and performance of the product. The Standard configuration is designed to fit most application needs and the Electrical Specification table shows parameter values of functionality and performance with the Standard configuration, unless otherwise specified. Changes in Standard configuration might be required to optimize performance in specific applications. Changes to the Standard configuration are required for current sharing operation.

### **PRODUCT ELECTRICAL SPECIFICATION**

$T_{P1} = -30$  to +95 °C,  $V_I = 7.5$  to 14 V, unless otherwise specified under Conditions. Typical values given at:  $T_{P1} = +25$  °C,  $V_I = 12.0$  V, max  $I_o$ , unless otherwise specified under Conditions.  $V_o$  defined by pin strap. Standard configuration. External  $C_{IN} = 1000 \ \mu\text{F}/12 \ m\Omega + 24 \times 10 \ \mu\text{F}$ ,  $C_{OUT} = 10 \times 470 \ \mu\text{F}/5 \ m\Omega + 10 \times 100 \ \mu\text{F}$ . See Operating Information section for solutions for selection of capacitor types.

Sense pins are connected to load.

| parameter                                                                  | conditions/descrip      | otion                                                 | min  | typ               | max  | units                   |

|----------------------------------------------------------------------------|-------------------------|-------------------------------------------------------|------|-------------------|------|-------------------------|

| input voltage (V <sub>I</sub> )                                            |                         |                                                       | 7.5  |                   | 14   | V                       |

| input voltage rise time ( $V_{I}$ )                                        | monotonic               |                                                       |      |                   | 6    | V/ms                    |

| output voltage without<br>pin-strap (V <sub>o</sub> )                      |                         |                                                       |      | 1.2               |      | V                       |

| output voltage adjustment<br>range (V <sub>o</sub> )                       |                         |                                                       | 0.60 |                   | 1.8  | V                       |

| output voltage adjustment in-<br>cluding PMBus margining (V <sub>o</sub> ) |                         |                                                       | 0.54 |                   | 1.98 | V                       |

| output voltage set-point<br>resolution (V <sub>o</sub> )                   |                         |                                                       |      | 0.025             |      | %V <sub>0</sub>         |

| output voltage accuracy <sup>2</sup> (V <sub>o</sub> )                     | including line, load,   | temp                                                  | -1   |                   | 1    | %V <sub>0</sub>         |

| internal resistance +S/-S to<br>VOUT/GND (V <sub>o</sub> )                 |                         |                                                       |      | 47                |      | Ω                       |

| +S bias current ( $V_0$ )                                                  |                         |                                                       | -100 | 20                | 100  | μA                      |

| -S bias current (V <sub>o</sub> )                                          |                         |                                                       |      | 20                |      | μA                      |

| line regulation $(V_0)$                                                    | $I_o = max I_o$         | $V_{o} = 0.6 V$<br>$V_{o} = 1.0 V$<br>$V_{o} = 1.8 V$ |      | 2<br>2<br>2       |      | mV<br>mV<br>mV          |

| load regulation ( $V_0$ )                                                  | I <sub>0</sub> = 0~100% | $V_{o} = 0.6 V$<br>$V_{o} = 1.0 V$<br>$V_{o} = 1.8 V$ |      | 2<br>2<br>2       |      | mV<br>mV<br>mV          |

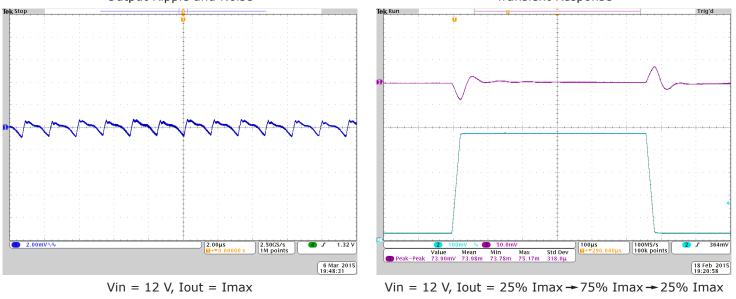

| output ripple & noise (V <sub>o</sub> )                                    | (up to 20 MHz)          | $V_{o} = 0.6 V$<br>$V_{o} = 1.0 V$<br>$V_{o} = 1.8 V$ |      | 2.5<br>3.5<br>5.0 |      | mVp-p<br>mVp-p<br>mVp-p |

| output current (I <sub>o</sub> )                                           |                         |                                                       | 0    |                   | 90   | А                       |

| current limit threshold (I <sub>lim</sub> )                                |                         |                                                       | 100  | 114               | 125  | Α                       |

2. For  $V_0 < 1.0$  V accuracy is +/-10 mV. For further deviations see section Output Voltage Adjust using PMBus

| parameter                                                                                          | conditions/description                                | l                                      | min         | typ                                    | max         | units                              |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|-------------|----------------------------------------|-------------|------------------------------------|

| short circuit current (I <sub>sc</sub> )                                                           | RMS, hiccup mode, $V_0 =$                             | 1.0 V, 1.5 mΩ short                    |             | 12                                     |             | А                                  |

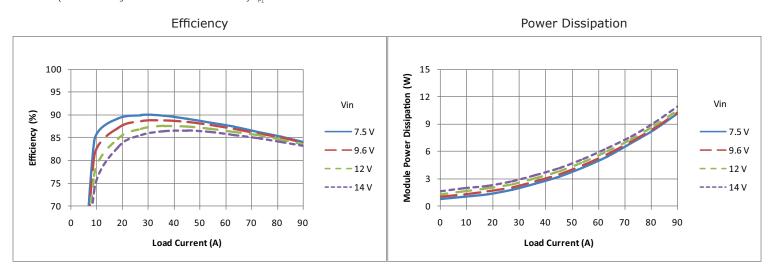

|                                                                                                    | Ŭ                                                     | $V_0 = 0.6 V$                          |             | 87.6                                   |             | %                                  |

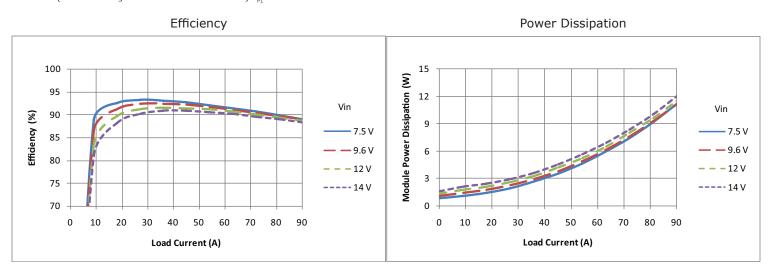

|                                                                                                    | 50% of max I <sub>o</sub>                             | $V_0 = 1.0 V$                          |             | 91.4                                   |             | %                                  |

| efficiency (η)                                                                                     |                                                       | $V_0^{\circ} = 1.8 V$                  |             | 94.3                                   |             | %                                  |

|                                                                                                    |                                                       | $V_{o} = 0.6 V$                        |             | 83.7                                   |             | %                                  |

|                                                                                                    | $I_o = max I_o$                                       | $V_{o} = 1.0 V$                        |             | 88.7                                   |             | %                                  |

|                                                                                                    |                                                       | $V_0^{\circ} = 1.8 V$                  |             | 92.5                                   |             | %                                  |

|                                                                                                    |                                                       | $V_{0} = 0.6 V$                        |             | 10.5                                   |             | W                                  |

| power dissipation at max $I_0(d)$                                                                  |                                                       | $V_{o}^{o} = 1.0 V$<br>$V_{o} = 1.8 V$ |             | 11.5<br>13.1                           |             | W<br>W                             |

|                                                                                                    |                                                       |                                        |             |                                        |             |                                    |

| input idling power (P <sub>1</sub> )                                                               | I – 0                                                 | $V_{o} = 0.6 V$<br>$V_{o} = 1.0 V$     |             | 1.29<br>1.35                           |             | W<br>W                             |

|                                                                                                    | $I_0 = 0$                                             | $V_0 = 1.0 V$<br>$V_0 = 1.8 V$         |             | 1.82                                   |             | Ŵ                                  |

| input standby power (P <sub>CTRI</sub> )                                                           | turned off with CTRL-pin                              | -0                                     |             | 0.44                                   |             | W                                  |

| switching frequency                                                                                |                                                       |                                        |             | 0111                                   |             |                                    |

| $(f_{sw} = 1/T_{sw})$                                                                              |                                                       |                                        |             | 320                                    |             | kHz                                |

| switching frequency range <sup>2</sup>                                                             | PMBus configurable                                    |                                        |             |                                        |             |                                    |

| $(f_{sw} = 1/T_{sw})$                                                                              | FREQUENCY_SWITCH                                      |                                        | 200         |                                        | 640         | kHz                                |

| switching frequency set-point                                                                      |                                                       |                                        |             |                                        |             |                                    |

| accuracy ( $f_{sw} = 1/T_{sw}$ )                                                                   |                                                       |                                        | -5          |                                        | 5           | %                                  |

| external sync pulse width                                                                          |                                                       |                                        |             |                                        |             |                                    |

| $(f_{SW} = 1/T_{SW})$                                                                              |                                                       |                                        | 150         |                                        |             | ns                                 |

| input clock frequency drift tol-                                                                   |                                                       |                                        |             |                                        |             |                                    |

| erance $(f_{sw} = 1/T_{sw})$                                                                       | external sync                                         |                                        | -10         |                                        | 10          | %                                  |

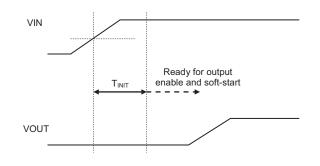

| initialization time (T <sub>INIT</sub> )                                                           | From VI > ~2.7 V to read                              | dy to be enabled                       |             | 67                                     |             | ms                                 |

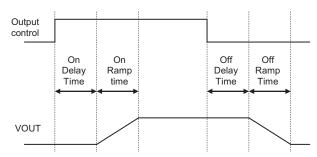

| output voltage                                                                                     | enabled by input voltage                              | <u>.</u> ·                             |             | T <sub>INIT</sub> + T <sub>ONdel</sub> |             |                                    |

| total on delay time (T <sub>oNdel_tot</sub> )                                                      | enabled by CTRL pin                                   |                                        |             |                                        |             |                                    |

|                                                                                                    | turn on delay duration                                |                                        |             | 5                                      |             | ms                                 |

| output voltage on delay time                                                                       | range PMBus configurable                              | e TON_DELAY                            | 3           |                                        | 250         | ms                                 |

| (T <sub>ONdel</sub> )                                                                              | accuracy (actual delay vs                             | set value)                             |             | -0/+2                                  |             | ms                                 |

| output voltage off delay time <sup>3</sup>                                                         | turn off delay duration                               |                                        |             | 0                                      |             | ms                                 |

| (T <sub>OFFdel</sub> )                                                                             | range PMBus configurable                              |                                        | 4           |                                        | 250         | ms                                 |

| ( OFFdel /                                                                                         | accuracy (actual delay vs                             | set value)                             |             | -0/+2                                  |             | ms                                 |

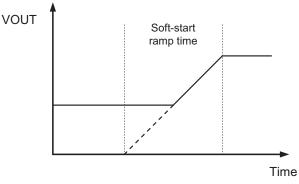

|                                                                                                    | turn on ramp duration                                 |                                        |             | 5                                      |             | ms                                 |

|                                                                                                    |                                                       |                                        | Disabled ir | n standard cor                         | figuration. |                                    |

| autout valtage en left ramp up                                                                     | turn off ramp duration                                |                                        |             | mediately upo                          |             |                                    |

| output voltage on/off ramp up<br>time $(0 \rightarrow 100\%, 100 \rightarrow 0\% \text{ of } V_0)$ |                                                       |                                        | 0           | f turn off dela                        | у.          |                                    |

| $(T_{ONrise}/T_{OFFfall})$                                                                         | ramp duration range PMB                               | Bus configurable                       | 0           |                                        | 100         | ms                                 |

|                                                                                                    | TON_RISE/TOFF_FALL                                    |                                        |             |                                        |             |                                    |

|                                                                                                    | ramp time accuracy for s<br>tual ramp time vs set val |                                        |             | 250                                    |             | μs                                 |

|                                                                                                    | •                                                     | ,                                      |             |                                        |             | 0/ \/                              |

| power good threshold (PG)                                                                          | rising<br>falling                                     |                                        |             | 90<br>85                               |             | %V <sub>0</sub><br>%V <sub>0</sub> |

|                                                                                                    | PMBus configurable                                    |                                        |             |                                        |             | / <b>°</b> ° 0                     |

| power good threshold range                                                                         | POWER_GOOD_ON                                         |                                        | 0           |                                        | 100         | %V <sub>0</sub>                    |

| (PG)                                                                                               | VOUT_UV_FAULT_LIMIT                                   |                                        | 0           |                                        | 200         |                                    |

1. Value refers to total (internal + external) effective output capacitance. Capacitance derating with VO typical for ceramic capacitors (bias characteristics) and temperature variations must be considered for the external capacitor(s). See section External Output Capacitors. Notes:

There are configuration changes to consider when changing the switching frequency, see section Switching Frequency.

The specified accuracy applies for off delay times larger than 4 ms. A value of 0 ms can be set to guarantee a fast shut-off, but this will force the device to Immediate Off behavior, even if soft-off, i.e. ramp-down, is configured. When setting 0 ms the actual delay will be 0 ms.

| barameter                                                                                                              | conditions/description                                                          | min    | typ     | max  | units           |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------|---------|------|-----------------|

| ower good delay (PG)                                                                                                   | From VO reaching target to PG assertion                                         |        | 2       |      | ms              |

| ower good delay range (PG)                                                                                             | PMBus configurable<br>POWER_GOOD_DELAY                                          | 0      |         | 5000 | ms              |

| nput under voltage protection<br>hreshold (IUVP)                                                                       |                                                                                 |        | 6.4     |      | V               |

| nput under voltage protection<br>hreshold range (IUVP)                                                                 | PMBus configurable<br>VIN_UV_FAULT_LIMIT                                        |        | 6.4~14  |      | V               |

| nput under voltage protection<br>nysteresis (IUVP)                                                                     |                                                                                 |        | 0.5     |      | V               |

| nput under voltage protection<br>nysteresis range (IUVP)                                                               | PMBus configurable<br>VIN_UV_WARN_LIMIT                                         |        | 0~7.6   |      | V               |

| nput under voltage protection<br>set point accuracy (IUVP)                                                             |                                                                                 |        | 280     |      | mV              |

| nput under voltage protection<br>esponse delay (IUVP)                                                                  |                                                                                 |        | 100     |      | μs              |

| input under voltage protection shutdown, automatic restart<br>fault response <sup>1</sup> (IUVP) VIN_UV_FAULT_RESPONSE |                                                                                 |        | 280     |      | ms              |

| nput over voltage protection<br>hreshold (IOVP)                                                                        |                                                                                 | 16     |         |      | V               |

| nput over voltage protection<br>hreshold range (IOVP)                                                                  | PMBus configurable<br>VIN_OV_FAULT_LIMIT                                        | 6.9~16 |         |      | V               |

| nput over voltage protection<br>hysteresis (IOVP)                                                                      |                                                                                 | 1      |         |      | V               |

| nput over voltage protection<br>hysteresis range (IOVP)                                                                | PMBus configurable<br>VIN_OV_WARN_LIMIT                                         |        | 0~9.1   |      | V               |

| nput over voltage protection<br>set point accuracy (IOVP)                                                              |                                                                                 |        | 280     |      | mV              |

| nput over voltage protection<br>esponse delay (IOVP)                                                                   |                                                                                 | 100    |         |      | μs              |

| nput over voltage protection<br>ault response <sup>1</sup> (IOVP)                                                      | shutdown, automatic restart<br>VIN_OV_FAULT_RESPONSE                            |        | 280     |      | ms              |

| output under voltage protection hreshold (UVP)                                                                         |                                                                                 |        | 85      |      | %V <sub>0</sub> |

| output under voltage protection<br>hreshold range (UVP)                                                                | PMBus configurable<br>VOUT_UV_FAULT_LIMIT                                       | 0~100  |         |      | %V <sub>0</sub> |

| output over voltage protection<br>hreshold (OVP)                                                                       |                                                                                 |        | 115     |      | %V <sub>0</sub> |

| utput over voltage protection<br>hreshold range (OVP)                                                                  | PMBus configurable<br>VOUT_OV_FAULT_LIMIT                                       |        | 100~115 |      | %V <sub>0</sub> |

| utput over/under<br>oltage protection response<br>ime (UVP/OVP)                                                        |                                                                                 |        | 10      |      | μs              |

| utput over/under<br>oltage protection fault<br>esponse <sup>1</sup> (UVP/OVP)                                          | shutdown, automatic restart<br>VOUT_UV_FAULT_RESPONSE<br>VOUT_OV_FAULT_RESPONSE |        | 280     |      | ms              |

Notes: 1. Automatic restart ~280 ms after fault if the fault is no longer present. Continuous restart attempts if the fault reappear after restart. See Operating Information for other fault response options.

| parameter                                                            | conditions/description                                         |                                                                                                                  | min     | typ                     | max       | unit            |

|----------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------|-------------------------|-----------|-----------------|

| over current protection<br>threshold <sup>1</sup> (OCP)              | set value per phase                                            |                                                                                                                  |         | 57                      |           | А               |

| over current protection<br>threshold range <sup>1</sup> (OCP)        | PMBus configurable<br>IOUT_AVG_OC_FAULT_LI                     | MIT                                                                                                              |         | 0~57                    |           | А               |

| over current protection<br>protection delay <sup>1</sup> (OCP)       |                                                                |                                                                                                                  |         | 5                       |           | T <sub>sw</sub> |

| over current protection<br>fault response <sup>1</sup> (OCP)         | shutdown, automatic rest<br>MFR_IOUT_OC_FAULT_RE               |                                                                                                                  |         | 280                     |           | ms              |

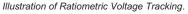

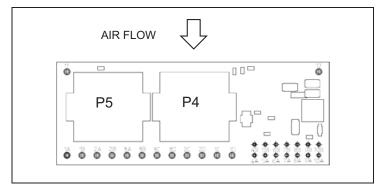

| over temperature protection threshold <sup>3</sup> (OTP)             | position P3                                                    |                                                                                                                  |         | 125                     |           | °C              |

| over temperature protection<br>hreshold range <sup>3</sup> (OTP)     | position P3<br>PMBus configurable<br>OT_FAULT_LIMIT            |                                                                                                                  |         | -40~125                 |           | °C              |

| over temperature protection<br>systeresis <sup>3</sup> (OTP)         | position P3<br>PMBus configurable                              |                                                                                                                  |         | 15                      |           | °C              |

| over temperature protection<br>fault response <sup>3</sup> (OTP)     | position P3<br>shutdown, automatic rest<br>OT_FAULT_RESPONSE   | art <sup>2</sup>                                                                                                 |         | 280                     |           | ms              |

| over temperature protection<br>hreshold <sup>3</sup> (OTP)           | position P1                                                    |                                                                                                                  |         | 150                     |           | °C              |

| over temperature protection<br>hreshold range <sup>3</sup> (OTP)     | position P1<br>PMBus configurable<br>MFR_VMON_OV_FAULT_L       | IMIT                                                                                                             |         | -40~150                 |           | °C              |

| over temperature protection<br>nysteresis <sup>3</sup> (OTP)         | position P1<br>PMBus configurable                              |                                                                                                                  |         | 25                      |           | °C              |

| over temperature protection<br>fault response <sup>3</sup> (OTP)     | position P1<br>shutdown, automatic rest<br>VMON_OV_FAULT_RESPO |                                                                                                                  |         | 280                     |           | ms              |

|                                                                      | input voltage<br>READ_VIN                                      |                                                                                                                  |         | 280                     |           | mV              |

|                                                                      | output voltage<br>READ_VOUT                                    |                                                                                                                  |         | 1                       |           | %V              |

| monitoring accuracy                                                  | output current<br>READ_IOUT                                    | $T_{_{P1}} = 25 \text{ °C}, V_{_{O}} = 1.0 \text{ V}$<br>$T_{_{P1}} = 0.95 \text{ °C}, V_{_{O}} = 1.0 \text{ V}$ |         | 1<br>3.5                |           | A<br>A          |

|                                                                      | duty cycle<br>READ_DUTY_CYCLE                                  | No tolerance, value is that applied to PWM controller                                                            |         |                         |           |                 |

|                                                                      | temperature<br>READ_TEMPERATURE_1                              | position P3                                                                                                      | -10     |                         | 5         | %               |

| tracking input bias current <sup>4</sup>                             | VTRK = 5 V                                                     |                                                                                                                  |         | 70                      | 200       | μA              |

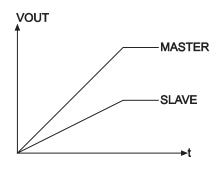

| racking input voltage range                                          | VTRK pin                                                       |                                                                                                                  |         | 0~1.8                   |           | V               |

| racking accuracy                                                     | regulation 100% tracking ramp accuracy, $V_0 = 1.0$ V          | V, 5 ms ramp                                                                                                     | -2      |                         | 2         | mV              |

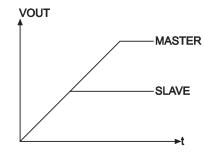

| current difference between<br>products in a current sharing<br>group | steady state operation                                         |                                                                                                                  | Max 2 x | READ_IOUT m<br>accuracy | onitoring |                 |

| number of products in a current<br>sharing group                     |                                                                |                                                                                                                  |         |                         | 4         |                 |

The set OCP limit applies per phase. The total OCP limit will be twice the set value.

Automatic restart ~280 ms after fault if the fault is no longer present. Continuous restart attempts if the fault reappear after restart. See Operating Information See section Over Temperature Protection (OTP).

The maximum tracking rise-time is 1 V/ms, see section Voltage Tracking.

| parameter                                                         | conditions/description                                      | min  | typ                       | max | units    |

|-------------------------------------------------------------------|-------------------------------------------------------------|------|---------------------------|-----|----------|

| logical output low signal level<br>(V <sub>oL</sub> )             | SCL, SDA, SYNC, DDC, SLRT, PG<br>sink/source current = 2 mA |      |                           | 0.5 | V        |

| ogical output high signal level<br>(V <sub>он</sub> )             | SCL, SDA, SYNC, DDC, SLRT, PG<br>sink/source current = 2 mA | 2.25 |                           |     | V        |

| logic output low sink current $(I_{OL})$                          |                                                             | -2   |                           |     | mA       |

| logic output high source cur-<br>rent ( $I_{ m OH}$ )             |                                                             |      |                           | 2   | mA       |

| logic input low threshold (V $_{\rm IL}$ )                        | SCL, SDA, CTRL, SYNC, DDC                                   |      |                           | 0.8 | V        |

| logic input high threshold ( $V_{IH}$ )                           | SCL, SDA, CTRL, SYNC, DDC                                   | 2    |                           |     | V        |

| logic leakage current ( $I_{I\_LEAK}$ )                           | SCL, SDA, SYNC, SLRT, PG                                    | -100 |                           | 100 | μA       |

| ogic pin input capacitance<br>(C <sub>I_PIN</sub> )               | SCL, SDA, CTRL, SYNC, DDC                                   |      | 12                        |     | pF       |

| logic pin internal pull-up resis-<br>tance (R <sub>I_PU</sub> )   | SCL, SDA, SLRT<br>CTRL to +5V<br>DDC to +5V                 | no   | internal pull<br>10<br>47 | -up | kΩ<br>kΩ |

| SMBus operating frequency $(f_{SMB})$                             |                                                             | 100  |                           | 400 | kHz      |

| SMBus bus free time <sup>1</sup> (T <sub>BUF</sub> )              | STOP bit to START bit                                       | 1.3  |                           |     | μs       |

| SMBus SDA setup time from<br>SCL <sup>1</sup> (t <sub>set</sub> ) |                                                             | 100  |                           |     | ns       |

| SMBus SDA hold time from<br>SCL <sup>1</sup> (t <sub>hold</sub> ) |                                                             | 300  |                           |     | ns       |

| SMBus START/STOP condition<br>setup/hold time from SCL            |                                                             | 600  |                           |     | ns       |

| SCL low period (T <sub>low</sub> )                                |                                                             | 1.3  |                           |     | μs       |

| SCL high period (T <sub>high</sub> )                              |                                                             | 0.6  |                           |     | μs       |

Notes: 1. See SMBus - Timing section.

.....

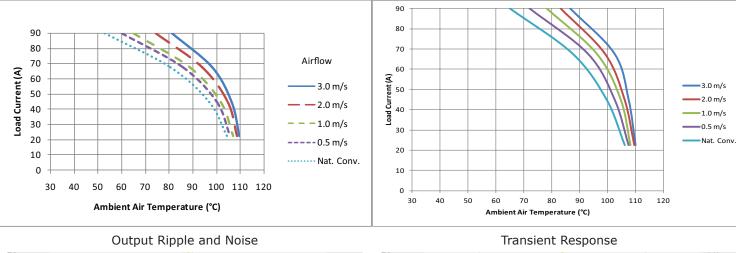

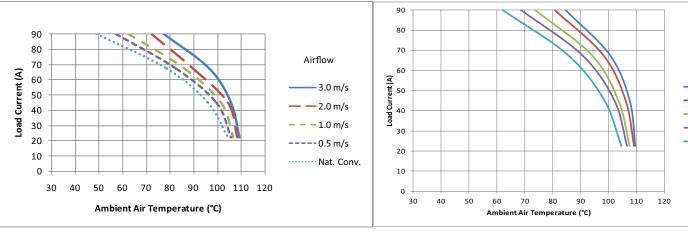

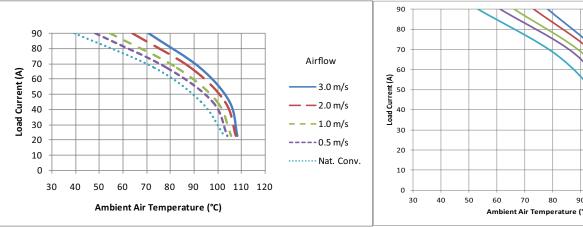

Output Current Derating for Lay Down Version

## TYPICAL OUTPUT CHARACTERISTICS, $V_0 = 0.6 V$

**Conditions** [Standard configuration unless otherwise stated]:  $T_{_{P1}}$  = 25°C

#### Output Current Derating for Vertical Version

3.0 m/s

2.0 m/s

1.0 m/s

0.5 m/s

Nat. Conv.

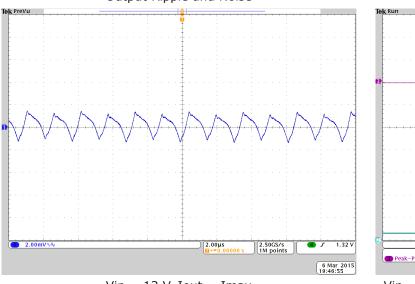

# TYPICAL OUTPUT CHARACTERISTICS, $V_0 = 1.0 V$

**Conditions** [Standard configuration unless otherwise stated]:  $T_{_{P1}}$  = 25°C

#### Output Current Derating for Vertical Version

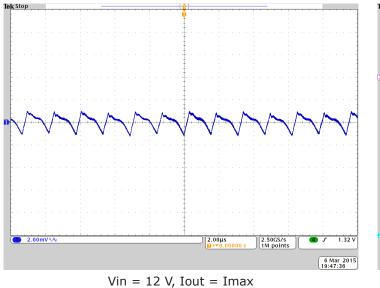

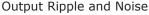

#### Output Ripple and Noise

.....

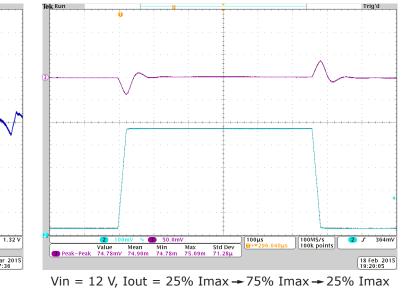

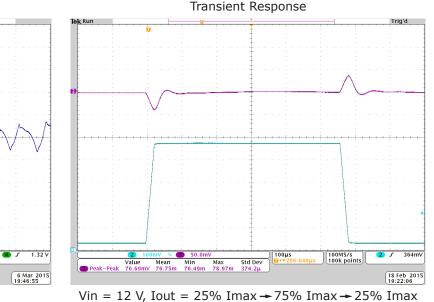

#### Transient Response

Output Current Derating for Lay Down Version

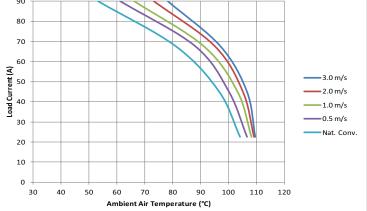

### TYPICAL OUTPUT CHARACTERISTICS, $V_0 = 1.8 V$

**Conditions** [Standard configuration unless otherwise stated]:  $T_{_{P1}}$  = 25°C

#### Output Current Derating for Vertical Version

Vin = 12 V, Iout = Imax

-----

Output Current Derating for Lay Down Version

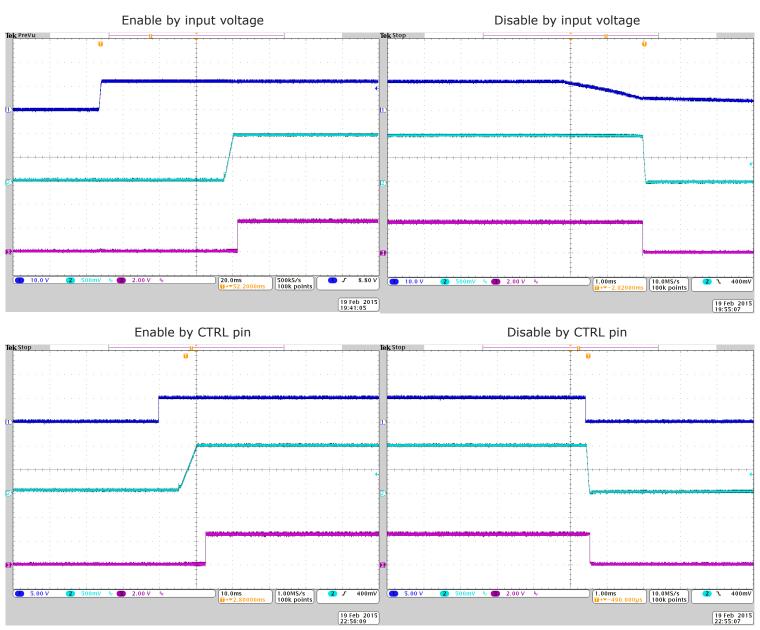

# **TYPICAL ON/OFF CHARACTERISTICS**

**Conditions** [Standard configuration unless otherwise stated]:  $T_{_{P1}}$  = 25°C,  $V_{_0}$  = 1.0 V

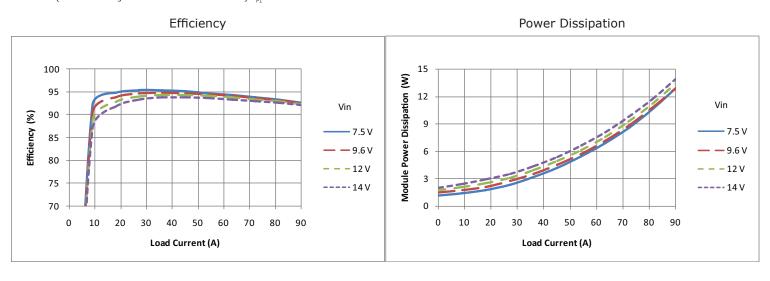

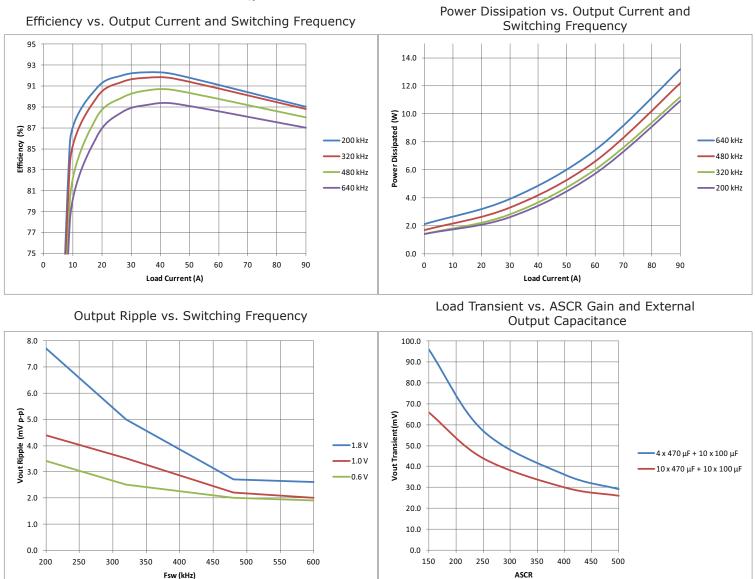

### **TYPICAL CHARACTERISTICS**

**Conditions** (Standard configuration unless otherwise stated):  $T_{p_1} = 25^{\circ}C$

.....

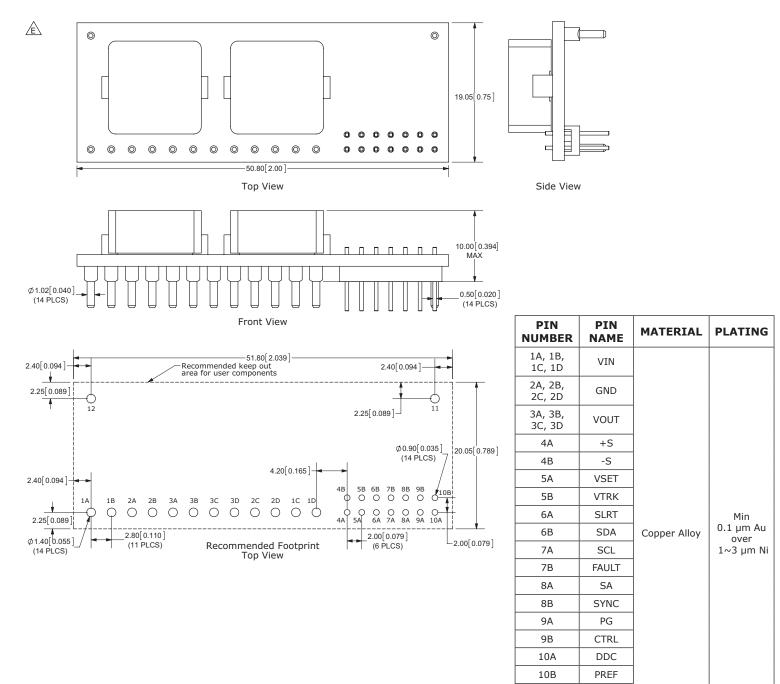

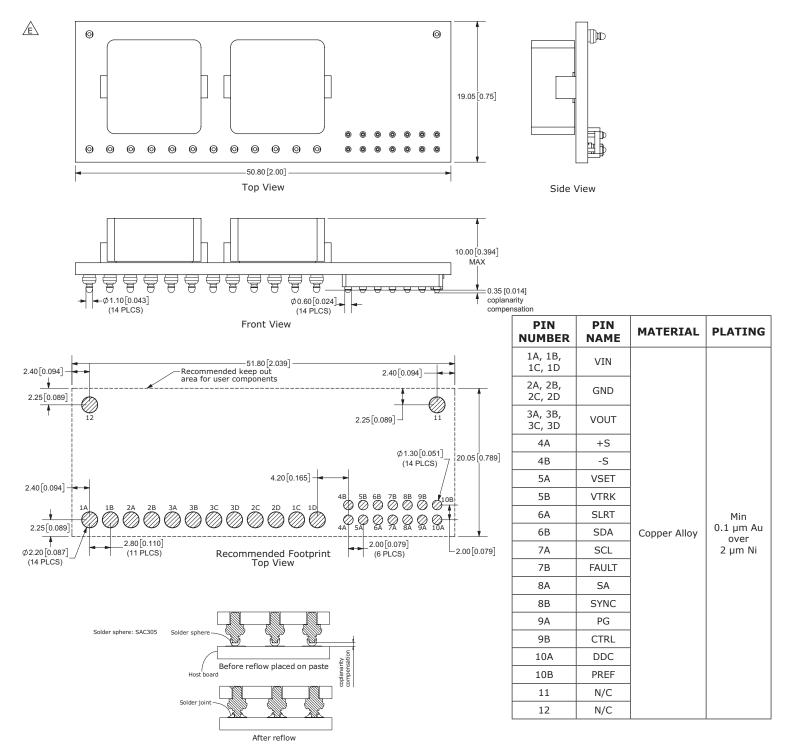

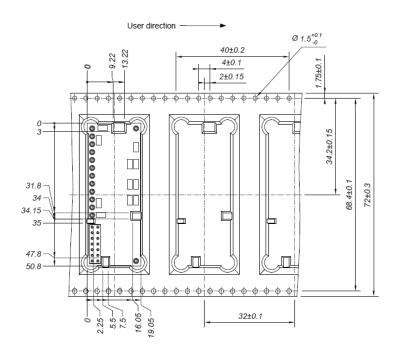

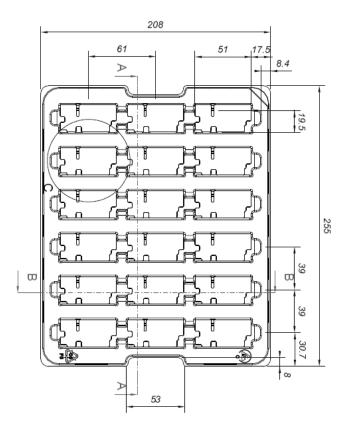

# MECHANICAL DRAWING (HORIZONTAL, THROUGH-HOLE MOUNT)

units: mm [inches] tolerance unless specified: X.X ±0.50 [0.02] X.XX ±0.25 [0.01] (not applied on footprint or typical values)

1. 0.19 mm [0.008 inches] minimum clearance components under POL module to host PCB. Note: ..... .....

.....

11

12

N/C

N/C

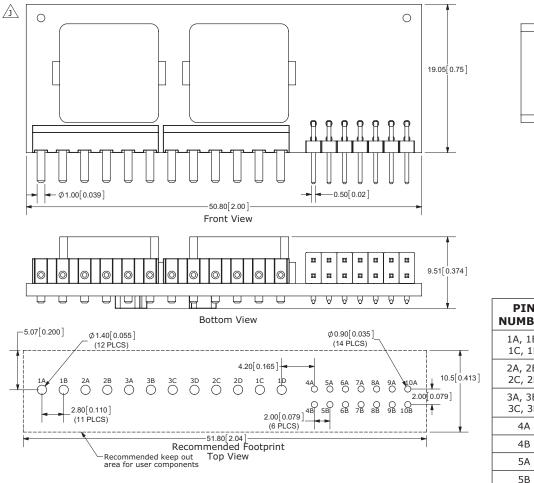

# **MECHANICAL DRAWING (HORIZONTAL, SURFACE MOUNT)**

units: mm [inches] tolerance unless specified: X.X  $\pm 0.50$  [0.02] X.XX  $\pm 0.25$  [0.01] (not applied on footprint or typical values)

# **MECHANICAL DRAWING (VERTICAL)**

units: mm [inches] tolerance unless specified: X.X  $\pm 0.50$  [0.02] X.XX  $\pm 0.25$  [0.01] (not applied on footprint or typical values)

.....

| U                 | IJ          |              |                   |

|-------------------|-------------|--------------|-------------------|

| Side              | e View      |              |                   |

|                   |             |              |                   |

|                   |             |              |                   |

| PIN<br>NUMBER     | PIN<br>NAME | MATERIAL     | PLATING           |

| 1A, 1B,<br>1C, 1D | VIN         |              |                   |

| 2A, 2B,<br>2C, 2D | GND         |              |                   |

| 3A, 3B,<br>3C, 3D | VOUT        |              |                   |

| 4A                | +S          |              |                   |

| 4B                | -S          |              |                   |

| 5A                | VSET        |              |                   |

| 5B                | VTRK        |              | Min               |

| 6A                | SLRT        | Copper Alloy | 0.1 µm Au<br>over |

| 6B                | SDA         |              | 1~3 µm Ni         |

| 7A                | SCL         | ]            |                   |

| 7B                | FAULT       | ]            |                   |

| 8A                | SA          | ]            |                   |

| 8B                | SYNC        | ]            |                   |

| 9A                | PG          | ]            |                   |

| 9B                | CTRL        | ]            |                   |

| 10A               | DDC         | ]            |                   |

| 10B               | PREF        | ]            |                   |

ہ م

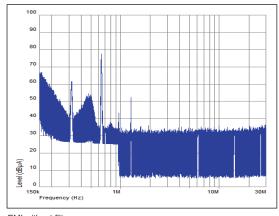

# **EMC SPECIFICATION**

Conducted EMI is measured according to the test set-up below. The typical fundamental switching frequency is 320 kHz.

#### **Conducted EMI**

Input terminal value (typical for standard configuration).  $V_{_{\rm T}}$  = 12 V,  $V_{_{\rm O}}$  = 1.0 V,  $I_{_{\rm O}}$  =  $I_{_{\rm MAX}}$

EMI without filter.

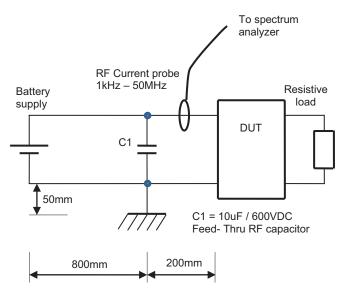

Test set-up conducted emission, power lead.

#### **Output Ripple and Noise**

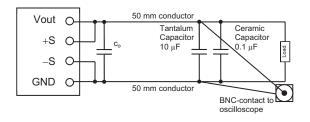

The circuit shown below is used to measure output ripple and noise. A damped filter is created by the 50 mm conductor and the two capacitors.

Output ripple and noise test set-up.

The following is an example of the low frequency output ripple and noise as measured with the above circuit.

| an dakimer           | Antonia Antonia  | unication    | ninkaniiki                                                                                                       | Réferences                                                                                                     | Normiate         | 1999 Contraction |             | elbianus    |             |

|----------------------|------------------|--------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------|------------------|-------------|-------------|-------------|

| nu frati na frati di | n fisikali (kala | ana selfeset | and the second | en anter | alidadica survey | on ntá útal      | ann san Rei | tones water | han indered |

|                      |                  |              |                                                                                                                  |                                                                                                                |                  |                  |             |             |             |

|                      |                  |              |                                                                                                                  |                                                                                                                |                  |                  |             |             |             |

V,=12 V, V<sub>o</sub>=1.0 V, I<sub>o</sub>=90 A, C<sub>out</sub> = 10 x 470  $\mu$ F/5 m $\Omega$  + 10 x 100  $\mu$ F, 5 mV/div, 50  $\mu$ s/div

Example of low frequency ripple at the output.

### **PMBUS INTERFACE**

#### **Power Conversion Overview**

The NDM3Z-90 module has several features to enable high power conversion efficiency. Adaptive algorithms and cycle-by-cycle charge management improves the response time and reduces the output deviation as a result of load transients. The incorporation of DFM enhances the CUI modules for improved performance.

#### **Power Management Overview**

This product incorporates a wide range of configurable power management features that are simple to implement with a minimum of external components. Additionally, the product includes protection features that continuously safeguard the load from damage due to unexpected system faults.

The product's standard configuration is suitable for a wide range of operation in terms of input voltage, output voltage, and load. The configuration is stored in an internal Non-Volatile Memory (NVM). All power management functions can be reconfigured using the PMBus interface. Throughout this document, different PMBus commands are referenced. A detailed description of each command is provided in the appendix at the end of this specification. The ability of CUI modules to digitally control, configure and monitor OS features provides significant benefits during development, production and the product life.

#### **SMBus Interface**

The product can be used with any standard two-wire I2C or SMBus host device. See Electrical Specification for allowed clock frequency range. In addition, the product is compatible with PMBus version 1.2 and includes an SLRT line to help mitigate limitations related to continuous fault monitoring. The PMBus signals SCL, SDA and SLRT require passive pull-up resistors as stated in the SMBus Specification. Pull-up resistors are required to guarantee the rise time as follows:

$T = R_p C_p \le 1 \mu s$

Where  $R_p$  is the pull-up resistor value and  $C_p$  is the bus loading. The maximum allowed bus load is 400 pF. The pull-up resistor should be tied to an external supply voltage in range from 2.5 to 5.5 V, which should be present prior to or during power-up. If the proper power supply is not available, voltage dividers may be applied. Note that in this case, the resistance in the equation above corresponds to parallel connection of the resistors forming the voltage divider.

#### **PMBus Addressing**

The PMBus address is configured with a resistor connected between the SA pin and the PREF pin, as shown in the Typical Application Circuit. Recommended resistor values are shown in the table below. 1% tolerance resistors are required.

| R <sub>sa</sub> (kΩ) | Address | R <sub>sa</sub> (kΩ) | Address |

|----------------------|---------|----------------------|---------|

| 0 (short)            | 0x26    | 42.2                 | 0x28    |

| 10                   | 0x19    | 46.4                 | 0x29    |

| 11                   | 0x1A    | 51.1                 | 0x2A    |

| 12.1                 | 0x1B    | 56.2                 | 0x2B    |

| 13.3                 | 0x1C    | 61.9                 | 0x2C    |

| 14.7                 | 0x1D    | 68.1                 | 0x2D    |

| 16.2                 | 0x1E    | 75                   | 0x2E    |

| 17.8                 | 0x1F    | 82.5                 | 0x2F    |

| 19.6                 | 0x20    | 90.9                 | 0x30    |

| 21.5                 | 0x21    | 100                  | 0x31    |

| 23.7                 | 0x22    | 110                  | 0x32    |

| 26.1                 | 0x23    | 121                  | 0x33    |

| 28.7                 | 0x24    | 133                  | 0x34    |

| 31.6                 | 0x25    | 147                  | 0x35    |

| 34.8                 | 0x26    | 162                  | 0x36    |

| 38.3                 | 0x27    | 178                  | 0x37    |

|                      |         | infinite (open)      | 0x28    |

#### **Reserved Addresses**

Addresses listed in the table below are reserved or assigned according to the SMBus specification and may not be usable. Refer to the SMBus specification for further information.

| Address     | Comment                                                   |

|-------------|-----------------------------------------------------------|

| 0x00        | general call address / START byte                         |

| 0x01        | CBUS address                                              |

| 0x02        | address reserved for different bus format                 |

| 0x03 ~ 0x07 | reserved for future use                                   |

| 0x08        | SMBus host                                                |

| 0x09 ~0x0B  | assigned for smart battery                                |

| 0x0C        | SMBus alert response address                              |

| 0x28        | reserved for ACCESS.bus host                              |

| 0x2C ~ 0x2D | reserved for previous versions of the SMBus specification |

| 0x37        | reserved for ACCESS.bus default address                   |

| 0x40 ~ 0x44 | reserved by previous versions of the SMBus specification  |

| 0x48 ~ 0x4B | unrestricted addresses                                    |

| 0x61        | SMBus device default address                              |

| 0x78 ~ 0x7B | 10-bit slave addressing                                   |

| 0x7C ~ 0x7F | reserved for future use                                   |

#### **Monitoring via PMBus**

It is possible to continuously monitor a wide variety of parameters through the PMBus interface. These include, but are not limited to, the parameters listed in the table below.

| Parameter                              | PMBus Command            |  |

|----------------------------------------|--------------------------|--|

| input voltage                          | READ_VIN                 |  |

| output voltage                         | READ_VOUT                |  |

| total output current                   | READ_IOUT                |  |

| output current of each phase           | READ_IOUT0<br>READ_IOUT1 |  |

| controller temperature                 | READ_TEMPERATURE_1       |  |

| switching frequency                    | READ_FREQUENCY           |  |

| duty cycle                             | READ_DUTY_CYCLE          |  |

| highest temperature of power switches* | READ_VMON                |  |

\* Reports a voltage level corresponding to the temperature. See command details in the end of this specification.

#### **Monitoring Faults**

Fault conditions can be monitored using the SLRT pin, which will be asserted low when any number of pre-configured fault or warning conditions occur. The SLRT pin will be held low until faults and/or warnings are cleared by the CLEAR\_FAULTS command, or until the output voltage has been re-enabled. It is possible to mask which fault conditions should not assert the SLRT pin by the command MFR\_SMBALERT\_MASK.

In response to the SLRT signal, the user may read a number of status commands to find out what fault or warning condition occurred, see table below.

| Fault & Warning Status | PMBus Command              |  |

|------------------------|----------------------------|--|

| overview, power good   | STATUS_WORD<br>STATUS_BYTE |  |

| output voltage level   | STATUS_VOUT                |  |

| output current level   | STATUS_IOUT                |  |

| input voltage level    | STATUS_INPUT               |  |

| temperature level      | STATUS_TEMPERATURE         |  |

| PMBus communication    | STATUS_CML                 |  |

| miscellaneous          | STATUS_MFR_SPECIFIC        |  |

#### **Snapshot Parameter Capture**

This product offers a special feature that enables the user to capture parametric data during normal operation by a single PMBus command SNAPSHOT. The following parameters are stored:

- Input voltage

- Output voltage

- Output current

- Controller temperature

- Switching frequency

- Duty cycle

- Status and fault information

When a fault occurs the Snapshot functionality will automatically store this parametric data to NVM. The data can then later be read back to provide valueable information for analysis. It is possible to select which faults will trigger a store to NVM by the PMBus command SNAPSHOT\_FAULT\_MASK.

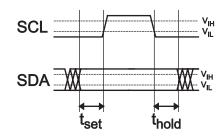

#### PMBus/I<sup>2</sup>C Timing

Setup and hold times timing diagram.

The setup time,  $t_{set}$ , is the time data, SDA, must be stable before the rising edge of the clock signal, SCL. The hold time  $t_{hold}$ , is the time data, SDA, must be stable after the falling edge of the clock signal, SCL. If these times are violated incorrect data may be captured or meta-stability may occur and the bus communication may fail. All standard SMBus protocols must be followed, including clock stretching. Refer to the SMBus specification for SMBus electrical and timing requirements.

This product supports the BUSY flag in the status commands to indicate product being too busy for SMBus response. A busfree time delay according to this specification must occur between every SMBus transmission (between every stop & start condition). The product supports PEC (Packet Error Checking) according to the SMBus specification.

When sending subsequent commands to the same unit it is recommended to insert additional delays after write transactions according to the table below. After read transactions a delay of 2 ms should be inserted before accessing the unit again.

| PMBus Command       | Delay after <i>write</i> before<br>additional command |  |

|---------------------|-------------------------------------------------------|--|

| STORE_USER_ALL      | 100 ms                                                |  |

| STORE_DEFAULT_ALL   | 100 ms                                                |  |

| RESTORE_USER_ALL    | 100 ms                                                |  |

| RESTORE_DEFAULT_ALL | 100 ms                                                |  |

| any other command   | 10 ms                                                 |  |

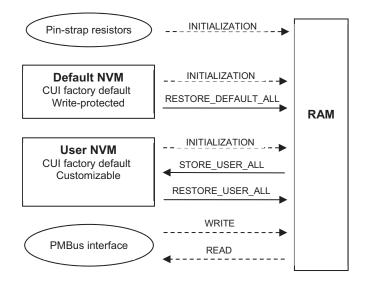

#### Non-Volatile Memory (NVM)

The product incorporates two Non-Volatile Memory areas for storage of the PMBus command values; the Default NVM and the User NVM. The Default NVM is pre-loaded with CUI factory default values. The Default NVM is write-protected and can be used to restore the CUI factory default values through the command RESTORE\_DEFAULT\_ALL. The User NVM is pre-loaded with CUI factory default values. The User NVM is writable and open for customization. The values in NVM are loaded during initialization according to section Initialization Procedure, whereafter commands can be changed through the PMBus Interface. The STORE\_USER\_ ALL command will store the changed parameters to the User NVM.

Illustration of memory areas of the product.

#### **Command Protection**

The user may write-protect specific PMBus commands in the User NVM by using the command UNPROTECT.

#### **Initialization Procedure**

The product follows an internal initialization procedure after power is applied to the VIN pin:

- 1. Self test and memory check.

- 2. The address pin-strap resistors are measured and the associated PMBus address is defined.

- The output voltage pin-strap resistor is measured and the associated output voltage level will be loaded to operational RAM of PMBus command VOUT\_COMMAND.

- CUI factory default values stored in default NVM memory are loaded to operational RAM. This overwrites any previously loaded values.

- Values stored in the User NVM are loaded into operational RAM memory. This overwrites any previously loaded values (e.g. VOUT\_COMMAND by pin-strap).

- 6. Check for external clock signal at the SYNC pin and lock internal clock to the external clock if used.

Once this procedure is completed and the Initialization Time has passed (see Electrical Specification), the output voltage is ready to be enabled using the CTRL pin. The product is also ready to accept commands via the PMBus interface, which in case of writes will overwrite any values loaded during the initialization procedure.

Illustration Initialization time.

### **OPERATING INFORMATION**

#### Input Voltage

The input voltage range 7.5-14V makes the product easy to use in intermediate bus applications when powered by a non-regulated bus converter or a regulated bus converter.

#### Input Under Voltage Protection (IUVP)

The product monitors the input voltage and will turn-on and turn-off at configured thresholds (see Electrical Specification). The turn-on input voltage threshold is set higher than the corresponding turn-off threshold. Hence, there is a hysteresis between turn-on and turn-off input voltage levels. Once the input voltage falls below the turn-off threshold, the device can respond in several ways as follows:

- 1. Immediate and definite shutdown of output voltage until the fault is cleared by PMBus command CLEAR\_FAULTS or the output voltage is re-enabled.

- Immediate shutdown of output voltage while the input voltage is below the turn-on threshold.

Operation resumes automatically and the output is enabled when the input voltage has risen above the turn-on threshold.

The default response is option 2. The IUVP function can be reconfigured using the PMBus commands VIN\_UV\_FAULT\_LIMIT (turn-off threshold), VIN\_UV\_WARN\_LIMIT (turn-on threshold) and VIN\_UV\_FAULT\_RESPONSE.

#### Input Over Voltage Protection (IOVP)

The product monitors the input voltage continously and will respond as configured when the input voltage rises above the configured threshold level (see Electrical Specification). Refer to section "Input Under Voltage Protection" for functionality, response configuration options and default setting. The IOVP function can be reconfigured using the PMBus commands VIN\_OV\_FAULT\_LIMIT (turn-off threshold), VIN\_OV\_WARN\_LIMIT (turn-on threshold) and VIN\_OV\_FAULT\_RESPONSE.

#### Input and Output Impedence

The impedance of both the input source and the load will interact with the impedance of the product. It is important that the input source has low characteristic impedance. If the input voltage source contains significant inductance, the addition of a capacitor with low ESR at the input of the product will ensure stable operation.

#### **External Input Capacitors**

The product is a two-phase converter which gives lower input ripple than a single phase design. Thus, ripple-current-rating requirements for the input capacitors are lower.

For most applications non-tantalum capacitors are preferred due to the robustness of such capacitors to accommodate high inrush currents of systems being powered from very low impedance sources. It is recommended to use a combination of ceramic capacitors and low-ESR electrolytic/ polymer bulk capacitors. The low ESR of ceramic capacitors effectively limits the input ripple voltage level, while the bulk capacitance minimizes deviations in the input voltage at large load transients.

If several products are connected in a phase spreading setup the amount of input ripple current, and capacitance per product, can be reduced.

Input capacitors must be placed closely and with low impedance connections to the VIN and GND pins in order to be effective.

#### **External Output Capacitors**

The output capacitor requirement depends on two considerations; output ripple voltage and load transient response. To achieve low ripple voltage, the output capacitor bank must have a low ESR value, which is achieved with ceramic output capacitors. A low ESR value is critical also for a small output voltage deviation during load transients. Designs with smaller load transients can use fewer capacitors and designs with more dynamic load content will require more load capacitors to achieve a small output deviation. Improved transient response can also be achieved by adjusting the settings of the control loop of the product. Adding output capacitance decreases loop band-width.

It is recommended to locate low ESR ceramic and low ESR electrolytic/polymer capacitors as close to the load as possible, using several capacitors in parallel to lower the effective ESR. It is important to use low resistance and low inductance PCB layouts and cabling in order for capacitance to be effective.

#### Dynamic Loop Compensation (DLC)

The typical design of regulated power converters includes a control function with a feedback loop that can be closed using either analog or digital circuits. The feedback loop

is required to provide a stable output voltage, but should be optimized for the output filter to maintain output voltage regulation during transient conditions such as sudden changes in output current and/or input voltage. Digitally controlled converters allow one to optimize loop parameters without the need to change components on the board, however, optimization can still be challenging because the key parameters of the output filter include parasitic impedances in the PCB and the often distributed filter components themselves.

Dynamic Loop Compensation has been developed to solve the problem of compensation for a converter with a difficult to define output filter. This task is achieved by utilization of algorithms that can identify an arbitrary output filter based on accurate measurements of the output voltage in response to a very small excitation signal initiated by the algorithm, or occurring due to the changes in operating conditions, and automatically adjust feedback loop parameters to match the output filter.

Details of the algorithm that is used to characterize an output filter and the different operational modes can be found in the following sections.

#### **Control Loop**

The products use a fully digital control loop that achieves precise control of the entire power conversion process, resulting in a very flexible device that is also very easy to use. A non-linear charge-mode control algorithm is implemented that responds to output current changes within a single PWM switching cycle, achieving a smaller total output voltage variation with less output capacitance than traditional PWM controllers, thus saving cost and board space. The algorithm is inherently stable at all conditions due to a residual scheme.

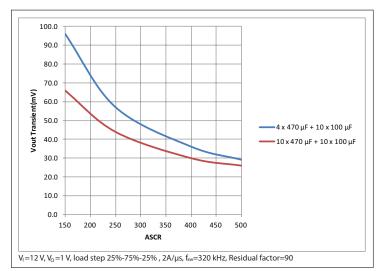

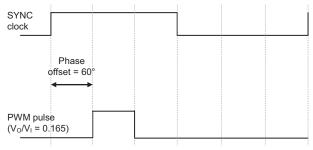

Control may be set more or less aggressive by adjusting a gain factor, set by the PMBus command ASCR\_CONFIG. Increasing the gain, i.e the control effort, will reduce the voltage deviation at load transients, at the expense of somewhat increased ripple on the output. Below graph exemplifies the impact on load transient performance when adjusting the gain factor.

Voltage deviation vs. control loop gain setting and output capacitance

The user may also adjust the residual factor, set by the ASCR\_CONFIG command, to improve the recovery time after a load transient.

Recovery time vs. control loop residual setting and output capacitance.

By default the product is configured with a moderate gain setting to provide a trade-off between load transient performance and output ripple for a wide range of operating conditions. For a specific application the gain factor can be increased with an improved load transient response.

#### **Remote Sense**

The product has remote sense to compensate the voltage drops between the output and the point of load. The sense traces should be located close to each other and to the PCB ground layer to reduce noise susceptibility.

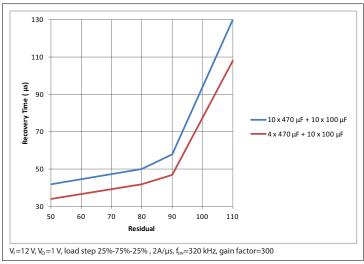

In cases where the external output filter includes an inductor (forming a pi filter) according to the picture below, the  $L_{EXT}/C_{EXT}$  resonant frequency places an upper limit on the controller loop bandwidth. If the resonant frequency is high the sense lines can be connected after the filter (as shown in the picture) – if the resonant frequency is low and the DC drop from  $L_{EXT}$  is acceptable, sensing before the filter may be better.

External output filter with inductor (pi filter).

#### **Output Voltage Control**

To control the output voltage the following options are available:

- 1. Output voltage is controlled through the CTRL pin.

- 2. Output voltage is controlled using the PMBus command OPERATION.

The CTRL pin has an internal 10 k $\Omega$  pull-up resistor to 5 V. The external device must provide a minimum required sink current to guarantee a voltage not higher than the logic low threshold level (see Electrical Characteristics). When the CTRL pin is left open, the voltage generated on the CTRL pin is 5 V.

If the device is to be synchronized to an external clock source, the clock frequency must be stable prior to enabling the output voltage. **Output Voltage Adjust using Pin-Strap Resistor**

Using an external Pin-strap resistor,  $R_{SET}$ , the output voltage can be set to several predefined levels shown in the table below. The resistor should be applied between the VSET pin and the PREF pin as shown in the Typical Application Circuit. Maximum 1% tolerance resistors are required.

| R <sub>set</sub> (kΩ) | Vout [V] | R <sub>set</sub> (kΩ) | Vout [V] |

|-----------------------|----------|-----------------------|----------|

| 0 (short)             | 1.00     | 26.1                  | 1.10     |

| 10                    | 0.60     | 28.7                  | 1.15     |

| 11                    | 0.65     | 31.6                  | 1.20     |

| 12.1                  | 0.70     | 34.8                  | 1.25     |

| 13.3                  | 0.75     | 38.3                  | 1.30     |

| 14.7                  | 0.80     | 42.2                  | 1.40     |

| 16.2                  | 0.85     | 46.4                  | 1.50     |

| 17.8                  | 0.90     | 51.1                  | 1.60     |

| 19.6                  | 0.95     | 56.2                  | 1.70     |

| 21.5                  | 1.00     | 61.9                  | 1.80     |

| 23.7                  | 1.05     | infinite (open)       | 1.20     |

RSET also sets the maximum output voltage; see section Output Voltage Range Limitation. The resistor is sensed only during the initialization procedure after application of input voltage. Changing the resistor value during normal operation will not change the output voltage.

#### **Output Voltage Adjust using PMBus**

The output voltage set by pin-strap can be overridden up to a certain level (see section Output Voltage Range Limitation) by using the PMBus command VOUT\_COMMAND. See Electrical Specification for adjustment range.

#### Voltage Margining Up/Down

Using the PMBus interface it is possible to adjust the output voltage to one of two predefined levels above or below the nominal voltage setting in order to determine whether the load device is capable of operating over its specified supply voltage range. This provides a convenient method for dynamically testing the operation of the load circuit over its supply margin or range. It can also be used to verify the function of supply voltage supervisors. Margin limits of the nominal output voltage ±5% are default, but the margin limits can be reconfigured using the PMBus commands VOUT\_MARGIN\_LOW and VOUT\_MARGIN\_HIGH. Margining is activated by the command OPERATION and can be used regardless of the output voltage being enabled by the CTRL pin or by the PMBus.

#### **Output Voltage Trim**

The actual output voltage can be trimmed to optimize performance of a specific load by setting a non-zero value for PMBus command VOUT\_TRIM. The value of VOUT\_TRIM is summed with the nominal output voltage set by VOUT\_COMMAND, allowing for multiple products to be commanded to a common nominal value, but with slight adjustments per load.

#### **Output Voltage Range Limitation**

The output voltage range that is possible to set by configuration or by the PMBus interface is hardware limited by the pin-strap resistor  $R_{SET}$ . The maximum output voltage is set to 115% of the output value defined by  $R_{SET}$ . This protects the application circuit from an over voltage due to an accidental PMBus command.

The limitation applies to the actual regulated output voltage rather than to the configured value. Thus, it is possible to write and read back a VOUT\_COMMAND value higher than the limit, but the actual output voltage will be limited. The output voltage limit can be reconfigured to a lower value by writing the PMBus command VOUT\_MAX.

#### **Output Over Voltage Protection (OVP)**

The product includes over voltage limiting circuitry for protection of the load. The default OVP limit is 15% above the nominal output voltage. The product can be configured to respond in different ways to the output voltage exceeding the OVP limit:

- 1. Immediate and definite shutdown of output voltage until the fault is cleared by PMBus command CLEAR\_FAULTS or the output voltage is re-enabled.

- Immediate shutdown of output voltage followed by continous restart attempts of the output voltage with a preset interval ("hiccup" mode).

The default response is option 2. The OVP limit and fault response can be reconfigured using the PMBus commands VOUT\_OV\_FAULT\_LIMIT, VOUT\_OV\_FAULT\_RESPONSE and OVUV\_CONFIG.

#### **Output Under Voltage Protection (UVP)**

The product includes output under voltage limiting circuitry for protection of the load. The default UVP limit is 15% below the nominal output voltage. Refer to section Output Over Voltage Protection for response configuration options and default setting. The UVP limit and fault response can be reconfigured using the PMBus commands VOUT\_UV\_FAULT\_LIMIT and VOUT\_UV\_FAULT\_RESPONSE.

#### **Power Good**

The power good pin (PG) indicates when the product is ready to provide regulated output voltage to the load. During ramp-up and during a fault condition, PG is held low. By default, PG is asserted high after the output has ramped to a voltage above 90% of the nominal voltage, and deasserted if the output voltage falls below 85% of the nominal voltage. These thresholds may be changed using the PMBus commands POWER\_GOOD\_ON and VOUT\_UV\_FAULT\_LIMIT.

The time between when the POWER\_GOOD\_ON threshold is reached and when the PG pin is actually asserted is set by the PMBus command POWER\_GOOD\_DELAY. See Electrical Specification for default value and range.

By default the PG pin is configured as an open drain output but it is also possible to set the output in push-pull mode by the command USER\_CONFIG. The PG output is not defined during ramp up of the input voltage due to the initialization of the product.

#### **Over Current Protection (OCP)**

The product includes robust current limiting circuitry for protection at continuous overload. After ramp-up is complete the product can detect an output overload/short condition. The following OCP response options are available:

- 1. Immediate and definite shutdown of output voltage until the fault is cleared by PMBus command CLEAR\_FAULTS or the output voltage is re-enabled.

- Immediate shutdown of output voltage followed by continous restart attempts of the output voltage with a preset interval ("hiccup" mode).

The default response from an over current fault is option 2. Note that delayed shutdown is not supported. The load distribution should be designed for the maximum output short circuit current specified. The OCP limit and response can be reconfigured using the PMBus commands IOUT\_AVG\_OC\_FAULT\_LIMIT and MFR\_IOUT\_OC\_FAULT\_RESPONSE.

#### **Under Current Protection (UCP)**

The product includes robust current limiting circuitry for protection at continuous reversed current, due to a synchronous rectifier ability to sink current. Refer to section Over Current Protection for response configuration options and default setting. The UCP limit and response can be reconfigured using the PMBus commands IOUT\_AVG\_UC\_FAULT\_LIMIT and MFR\_IOUT\_UC\_FAULT\_RESPONSE.

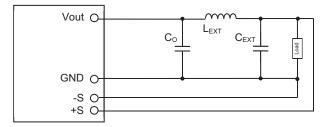

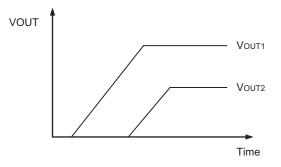

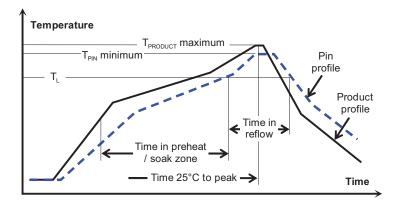

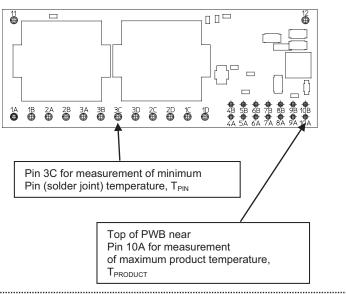

#### **Switching Frequency**