# NCV7381 FlexRay<sup>®</sup> Bus Driver Evaluation Board User's Manual

#### ON Semiconductor®

http://onsemi.com

#### **EVAL BOARD USER'S MANUAL**

#### Introduction

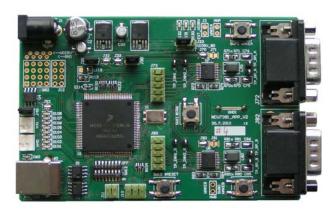

This document describes the NCV7381 APP V2 Evaluation board for the ON Semiconductor NCV7381 FlexRay<sup>®</sup> Bus Driver. The functionality and major parameters can be evaluated with the NCV7381\_APP\_v2 board.

The NCV7381 is a single-channel FlexRay<sup>®</sup> bus driver compliant with the FlexRay<sup>®</sup> Electrical Physical Layer Specification Rev. 3.0.1, capable of communicating at speeds of up to 10 Mb/s. It provides differential transmit and receive capability between a wired FlexRay<sup>®</sup> communication medium on one side and a protocol controller and a host on the other side.

NCV7381 mode control functionality is optimized for nodes permanently connected to car battery.

Additional details can be found in the NCV7381 datasheet.

The NCV7381\_APP\_V2 Evaluation board is a reference design for stand-alone 2-channel FlexRay<sup>®</sup> node. The board is intended to give designers easy, quick and convenient means for evaluation of NCV7381 FlexRay bus drivers. The design incorporates complete node solution with possibility of modifications and small board size. A set of two boards

allows users immediately start with the NCV7381 FlexRay Bus Driver. The MCU is preprogrammed with a firmware which provides simple mode control and FlexRay communication. With use of Freescale ™ BDM programmer and a suitable development environment, the MCU firmware can be freely modified and reprogrammed.

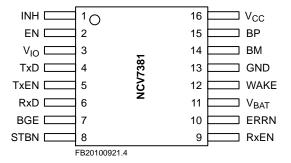

#### **NCV7381 Pin Connections**

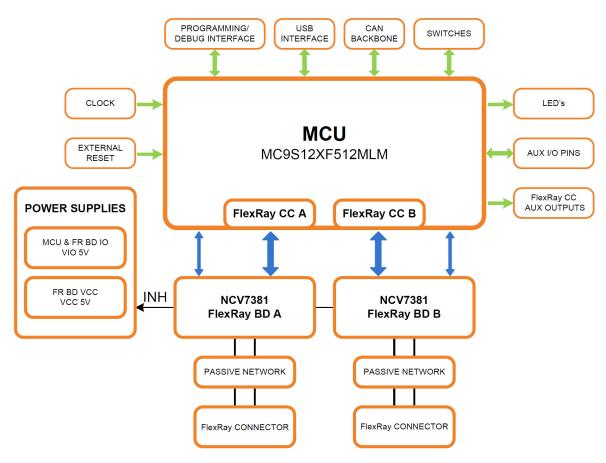

#### **Board Hardware**

The board consists of MCU with integrated 2-channel FlexRay communication controller interconnected with two separate FlexRay bus drivers (NCV7381), two switchable voltage regulators and peripherals. The board is prepared for various modifications in power supply concept and FlexRay bus termination, and allows simple extension of the system by unused MCU pins. USB interface provides compatibility with standard PC. The address of each board can be easily modified by address switch what allows creating complex FlexRay network without need of reprogramming the MCU. Implemented High Speed CAN interface can be used as a diagnostic interface in a network built from several nodes. For evaluation purposes NCV7381 is populated with several LED diodes and most of the bus driver signals are comfortable accessible to oscilloscope probes.

#### **GENERAL FEATURES**

#### FlexRay Transceiver

- Two Separate FlexRay® Channels with NCV7381 Bus Driver Compliant with the FlexRay Electrical Physical Layer Specification Rev. 3.0.1

- Reconfigurable Bus Termination End Node/Middle Node

- Common Mode Choke and Additional ESD Protection Footprint

- SUBD-9 Connectors FlexRay bus

- Local Wakeup Switch

#### MCU

- Freescale<sup>™</sup> 16-bit MC9S12XF Family MCU

- Integrated FlexRay Communication Controller (Protocol Specification Rev. 2.1)

- Integrated CAN 2.0 A, B Controller

- Background Debug Modul Single-wire Communication with Host Development System

- 512 kB Flash

- 32 kB RAM

- 50 MHz Maximum CPU Bus Frequency

- Relatively Small 112-pin LQFP Package

#### **Peripherals**

- Optical Isolated USB Interface (USB to UART Converter)

- Additional CAN Interface

- All NCV7381 Digital I/O Pins Connected to Test Points Easy Connection to Logic Analyzer

- 8 General Purpose LEDs

- Address Switch

#### Other

- Two Automotive Voltage Regulators with Inhibit Function (Input Battery Voltage Up to 42 V)

- Power Supplies Voltage Monitoring

- Instant 2-nodes FlexRay Network with Running Communication by Connecting Two NCV7381 EVBs

- PC Configuration Software under Development (Available upon Request)

#### **PCB Layout**

- The FlexRay Transceiver, the ESD Protection and the Common Mode Choke are Placed near to the FlexRay the ECU Connector

- The FlexRay Signal Lines (BP, BM) are Decoupled from Disturbances on the ECU Board

- The Routing of the FlexRay Lines (BP, BM, TX and TXEN) is Symmetric

- The Distance between the Lines BP and BM resp. TX and TXEN is Minimized

#### **GETTING STARTED**

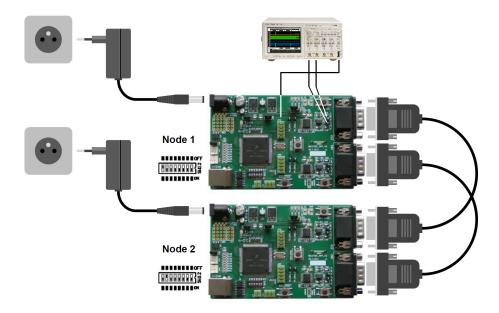

The NCV7381EVB board is fully assembled, pre-programmed and can be immediately used for evaluation. Only a few steps need be proceeded to get fully working simple FlexRay network.

Connect the evaluation boards as follows:

- 1. Set the boards to default configuration according to Jumpers and Default Configuration section

- 2. Set a different board address on each board. One of the boards must be set with address 1 and is considered as Master Board. Node address is configurable by address switch (SW12) see Address Switch section for details

- 3. Connect the boards according to figure below

- 4. Optionally connect an oscilloscope to any test-point as needed

- 5. After the power supply is applied, FlexRay communication is automatically initialized

With properly running setup, button SW11 (#IRQ) has following functions:

- Press the button shortly to read-out Bus Driver status register (Only in Bus Driver status indication mode)

- Press and hold the button for approximately 2 seconds to change LED bar indication mode. Three modes are available:

- FlexRay communication indication each LED is assigned to one slot according to LED number. The LED is blinking if the respective slot in FlexRay communication is active

- Bus Driver status indication Channel A,

- Bus Driver status indication Channel B:

- LED1 Local Wake-Up status

- LED2 Remote Wake-Up status

- LED3 TxEN-BGE Timeout status

- LED4 Bus Error status

- LED5 Vio Undervoltage status

- LED6 Vcc Undervoltage status

- LED7 Vbat Undervoltage status

- LED8 Power On status

- Press and hold the button for more than 5 seconds Both nodes are switched to SLEEP mode and can be woken-up by

one of the Local Wake-up switches. Only Node 1 is allowed to send the rest of network to SLEEP mode

In SLEEP mode, NCV7381 is supplied only from VBAT supply. VCC and VIO power supplies are switched off by NCV7381 INH output. MCU is not running and the board can be woken-up only with one of the Local Wakeup buttons (SW70, SW80).

- NCV7381 Local Wakeup function Wake-up one of the nodes by any Local Wakeup button

- NCV7381 Remote Wakeup function Second node is woken-up by Remote Wakeup pattern sent over the FlexRay bus by first node during initialization phase after Local Wakeup

#### **BOARD OVERVIEW**

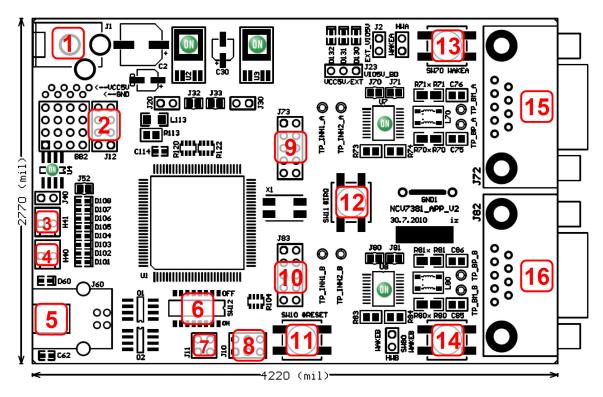

#### **Basic Interface**

#### Legend:

- 1 Power Supply Input Connector

- 2 Aux Digital I/O Connector

- 3 CAN Backbone Connector 1

- 4 CAN Backbone Connector 2

- 5 USB Interface

- 6 Address Switch

- 7 FlexRay CC Strobe Output Signals

- 8 BDM Connector (MCU Debugging Interface)

#### **Power Supply Input Connector**

Power supply input socket. Plug diameter 2.1 mm, length 14 mm. Maximum input voltage 42 V (Limited by onboard voltage regulators).

#### Aux Digital I/O Connector

These pin header contains 6 auxiliary MCU signals – one complete SPI interface (4 pins) and one UART interface (2 pins). These signals can be also used as general Input/Output signals for debugging or other purposes.

#### **CAN Backbone Connectors**

CAN backbone network is created as parallel connection of several boards. Each board contains two equivalent connectors in parallel, so whole network can be prepared using only simple point-to-point twisted pair.

- 9 FlexRay BD Signals Test Points (Channel A)

- 10 FlexRay BD Signals Test Points (Channel B)

- 11 MCU Reset Switch

- 12 MCU External Interrupt Switch

- 13 BD Local Wakeup Switch (Channel A)

- 14 BD Local Wakeup Switch (Channel B)

- 15 FlexRay Bus Connector (Channel A)

- 16 FlexRay Bus Connector (Channel B)

#### **USB** Interface

Standard B type USB socket is used for connection to PC. USB interface is bus powered and electrically isolated from the rest of the board, so it is not possible to supply this board via USB.

#### FlexRay CC Strobe Output Signals

The MCU FlexRay block provides a number of strobe signals for observing internal protocol timing related signals in the protocol engine.

| STBN1              | 0 | 0 | STBN3 |

|--------------------|---|---|-------|

| STBN0 <sub>5</sub> | 0 | 0 | STBN2 |

These signals are connected to STBN pin header:

#### **BDM Connector (MCU Debugging Interface)**

The BDM module provides a single-wire communication with host development system (Programming and debugging interface).

# BKGD O GND NC O O RESET NC O O VCC

#### FlexRay BD Digital Signals Test Points Headers

These headers are intended to be used as a test points for digital probes. Headers contain all FlexRay BD digital input and output signals.

Test points for both FlexRay channel A and channel B are placed on separated headers (J73 – channel A, J83 – channel B).

# GND GND EN O O TXD TXEN O O RXD BGE O O STBN ERRN O O RXEN

#### FlexRay BD Analog Signals Test Points

Each FlexRay channel contains 4 analog test points:

- INH1 Bus Driver Inhibit 1 output

- INH2 Bus Driver Inhibit 2 output

- BP FlexRay Bus Plus terminal

- BM FlexRay Bus Minus terminal

#### FlexRay Bus Connectors

FlexRay EPL Specification [1] does not prescribe certain connectors for FlexRay systems. Common used 9-pin D-Sub connectors were chosen as a suitable connector, whose electrical characteristics satisfy the specification.

**Table 1. FLEXRAY CONNECTOR**

| Pin # | Signal    | Description                 | Connection       | ESD Protection |

|-------|-----------|-----------------------------|------------------|----------------|

| 1     | -         | Reserved                    | Not Connected    |                |

| 2     | FR_BM     | BM Bus Line                 | BM               | Yes (Optional) |

| 3     | FR_GND    | Ground                      | GND              |                |

| 4     | -         | Reserved                    | Not Connected    |                |

| 5     | -         | Reserved                    | Not Connected    |                |

| 6     | -         | Reserved                    | Not Connected    |                |

| 7     | FR_BP     | BP Bus Line                 | BP               | Yes (Optional) |

| 8     | -         | Reserved                    | Not Connected    |                |

| 9     | (FR_Vbat) | Optional FR External Supply | Main Supply Line | Yes            |

Connector type: 9-pin D-Sub (DIN 41652 or corresponding international standard), plug (male)

#### **Jumpers and Default Configuration**

Figure 1. Jumpers and Soldering Straps

Table 2. 2-PIN JUMPER

| Open   |

|--------|

| Closed |

**Table 3. 3-PIN JUMPER**

| 1 2 3 |                     |

|-------|---------------------|

|       | Open                |

|       | Closed Position 1–2 |

|       | Closed Position 2–3 |

Table 4. NCV7381 EVB JUMPERS CONFIGURATION

| Jumper                  | Function                         | Configuration | Description                        | Default    |

|-------------------------|----------------------------------|---------------|------------------------------------|------------|

| 100                     | MOUNTO                           | Open          | Controlled by bd_INH1_x            | 0          |

| J20                     | J20 MCU VCC 5 V State            | Closed        | Always On                          | Open       |

|                         |                                  | Open          | BD VIO Disconnected                |            |

| J23                     | BC VIO Power Supply Selection    | Closed 1-2    | BD VIO Connected to MCU VCC        | Closed 1–2 |

|                         |                                  | Closed 2–3    | BD VIO – External VIO Power Supply |            |

| 120                     | DD VCC Ctata                     | Open          | Controlled by MCU                  | Classed    |

| J30 BD VCC State        | J30 BD VCC State                 | Closed        | Controlled by bd_INHx_x            | Closed     |

| 100                     | DD VCC labilities course (Ch. A) | Open          | bd_INH2_A                          | Classid    |

| J32                     | BD VCC Inhibit Source (Ch A)     | Closed        | bd_INH1_A                          | Closed     |

| 122                     | DD VCC labibit Source (Ch. D)    | Open          | bd_INH2_B                          | Closed     |

| J33                     | BD VCC Inhibit Source (Ch B)     | Closed        | bd_INH1_B                          | Closed     |

|                         | CAN Due Terreir etien            | Open          | Without Termination                | Classed    |

| J40                     | CAN Bus Termination              | Closed        | With 120 Ω Termination             | Closed     |

| IFO                     | Conoral Durnage LED              | Open          | LEDs Disabled                      | Closed     |

| J52 General Purpose LED | J52                              | Closed        | LEDs Enabled                       | Closed     |

**Table 4. NCV7381 EVB JUMPERS CONFIGURATION**

| Jumper | Function                          | Configuration | Description                 | Default |

|--------|-----------------------------------|---------------|-----------------------------|---------|

| J70    | IZO Discours (Oh A)               |               | BD VBAT Disconnected        | Closed  |

| 370    | Bus Driver VBAT Supply (Ch A)     | Closed        | BD VBAT Connected           | Closed  |

| 174    | Bug Driver \/DLIE Supply /Ch A\   | Open          | BD VBUF Disconnected        | Onen    |

| 371    | J71 Bus Driver VBUF Supply (Ch A) | Closed        | BD VBUF Connected to BD VCC | Open    |

| J80    | Bug Driver \/PAT Supply (Ch. P)   | Open          | BD VBAT Disconnected        | Closed  |

| 360    | Bus Driver VBAT Supply (Ch B)     | Closed        | BD VBAT Connected           | Closed  |

| 104    | J81 Bus Driver VBUF Supply (Ch B) | Open          | BD VBUF Disconnected        | Open    |

| JOI    |                                   | Closed        | BD VBUF Connected to BD VCC | Open    |

#### **Switches and Pushbuttons**

Figure 2. Switches Description

- SW10...MCU Reset button

- SW11...MCU External interrupt button

- SW12...8-way DIP switch. The function depends on the MCU program. As default ti it used for setting a node address

- SW70...FlexRay Transceiver Local Wakeup button (Channel A)

- SW80...FlexRay Transceiver Local Wakeup button (Channel B)

#### **Address Switch**

This switch is used for setting a node number. Each board is programmed with the same firmware, so every node in the network must be configured with different unique number.

#### Be careful:

LSB is situated on the left.

ON means the particular switch is closed and output is *Logical 0*!

OFF means the particular switch is open and output is *Logical 1*!

#### **MCU** Reset Button

This switch is used for generating low level at the MCU Reset pin. If MCU detects low level at the RESET pin external reset is performed.

#### **MCU External Interrupt Button**

The MCU interrupt module support one maskable interrupt input. This input is connected to SW11.

#### **BD Local Wakeup Buttons**

The FlexRay Bus drivers support Local Wakeup event detection. If a falling edge is recognized on WAKE pin, a local wakeup is detected. These switches (each for one FlexRay channel) are used for simulation of Local wakeup event normally generated by e.g. mechanical switch.

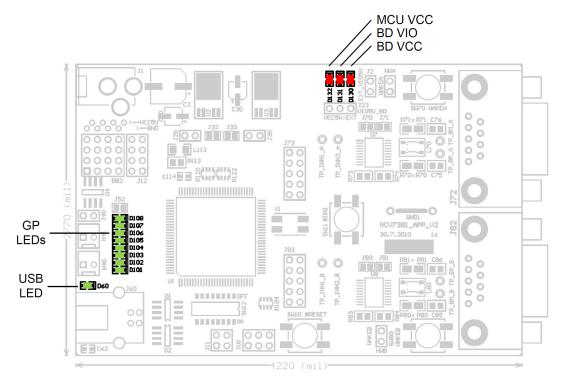

#### **LEDs**

Three power LEDs indicate proper function of voltage regulators. In case the MCU and the NCV7381 bus drivers IO cells use the same power supply (as by default) MCU VCC LED and BD VIO LED signalling is also the same.

The board contains a bank of eight general purpose LEDs (Green). Their function depends on the MCU program. There is also USB indication LED which is used to signal ongoing USB data transmission.

Figure 3. LEDs Description

#### **BLOCK DIAGRAM**

Figure 4. NCV7381 Evaluation Board Block Diagram

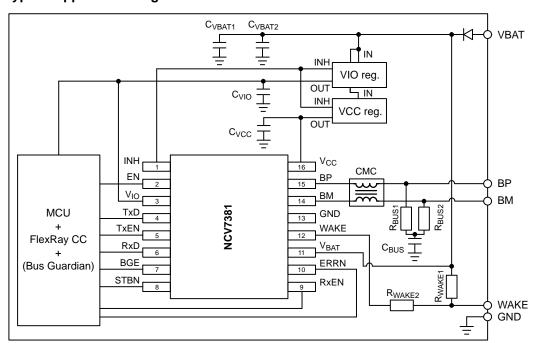

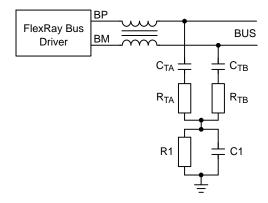

#### **NCV7381 Typical Application Diagram**

Figure 5. NCV7381 FlexRay Bus Driver Typical Application Diagram

| Component          | Function                                                                    | Min | Тур  | Max | Units |

|--------------------|-----------------------------------------------------------------------------|-----|------|-----|-------|

| C <sub>VBAT1</sub> | Decoupling Capacitor on Battery Line, Electrolytic                          |     | 10   |     | μF    |

| C <sub>VBAT2</sub> | Decoupling Capacitor on Battery Line, Ceramic (XR7)                         |     | 100  |     | nF    |

| C <sub>VCC</sub>   | Decoupling Capacitor on V <sub>CC</sub> Supply Line, Ceramic (XR7) (Note 1) |     | 100  |     | nF    |

| C <sub>VIO</sub>   | Decoupling Capacitor on V <sub>IO</sub> Supply Line, Ceramic (XR7) (Note 1) |     | 100  |     | nF    |

| R <sub>WAKE1</sub> | Pull-up Resistor on WAKE Pin                                                |     | 33   |     | kΩ    |

| R <sub>WAKE2</sub> | Serial Protection Resistor on WAKE Pin                                      |     | 3.3  |     | kΩ    |

| R <sub>BUS1</sub>  | Bus Termination Resistor (Note 2)                                           |     | 47.5 |     | Ω     |

| R <sub>BUS2</sub>  | Bus Termination Resistor (Note 2)                                           |     | 47.5 |     | Ω     |

| C <sub>BUS</sub>   | Common-mode Stabilizing Capacitor (Note 3)                                  |     | 4.7  |     | nF    |

| CMC                | Common-mode Chokes (Note 4)                                                 |     | 100  |     | μН    |

- 1. To improve EMC performance, 2.2 μF ceramic decoupling capacitor is recommended.

- 2. Type 1206 ±1%

- 3. Type  $0805 \pm 1\%$

- Recommended common-mode chokes: EPCOS B82789C0104N00x, EPCOS B82799C0104N001, TDK ACT45R-101-2P-TLxxx, TDK ACT45B-101-2P-TLxxx (x= don't care).

#### **SPECIFICATIONS**

#### **Power Supply**

The Evaluation board can be power either via DC power supply input socket with plug diameter 2.1 mm and length 14 mm or by one of the FlexRay bus connectors (See the connector description section). Maximum input voltage (42 V) is limited by on-board voltage regulators input voltage range.

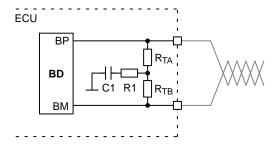

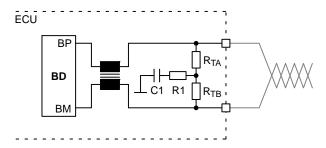

#### **Split Termination**

In order to achieve a better EMC performance, it is recommended to make use of a so-called split termination in all ECUs, where the Termination resistance  $R_T$  is split into two equal parts  $R_{TA}$  and  $R_{TB}$  [2].

Figure 6. ECU with Split Termination [2]

The serial RC combination  $(R_1; C_1)$  at the centre tap of the split termination provides a termination to GND for common mode signals.  $R_1$  is preferably omitted. Typical values are given in the following table:

**Table 5. TERMINATION PARAMETERS**

| Name                                                                            | Description                       | Тур  | Units |

|---------------------------------------------------------------------------------|-----------------------------------|------|-------|

| R1                                                                              | Resistor                          | < 10 | Ω     |

| C1                                                                              | Capacitor                         | 4700 | pF    |

| 2 x  R <sub>TA</sub> – R <sub>TB</sub>   / (R <sub>TA</sub> + R <sub>TB</sub> ) | Matching of Termination Resistors | ≤ 2  | %     |

For R<sub>TA</sub> and R<sub>TB</sub> the use of 1% tolerated resistors leads to a matching of 2%.

The better the matching of the split termination resistors  $R_{TA}$  and  $R_{TB}$ , the lower the electromagnetic emission.

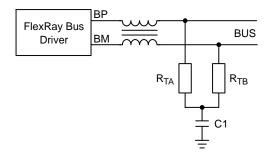

#### **Standard Termination**

Recommended bus split termination is shown in the Figure 7. Considering passive network, without active stars, proper termination should be applied at the two nodes that have the maximum electrical distance on the bus. The sum of termination resistors values should match the nominal cable impedance. At other nodes a high ohmic split termination should be applied.

Figure 7. Basic Split Termination

**Table 6. BASIC SPLIT TERMINATION PARAMETERS**

|                                   |                       | Value    |             |       |

|-----------------------------------|-----------------------|----------|-------------|-------|

| Name                              | Description           | End Node | Middle Node | Units |

| R <sub>TA</sub> , R <sub>TB</sub> | Termination Resistors | 47       | 1300        | Ω     |

| C1                                | Capacitor             | 4700     | 4700        | pF    |

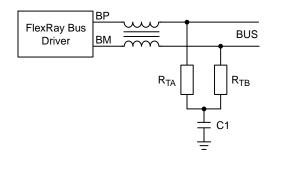

#### **Custom Termination**

In some cases a specific termination topology is required for middle modes. Such a termination connection and typical values are shown in Figure 9 and Table 7.

Figure 8. End Node Split Termination

Figure 9. Middle Node Split Termination

**Table 7. CUSTOM SPLIT TERMINATION PARAMETERS**

|                                   |                        | Value    |             |       |

|-----------------------------------|------------------------|----------|-------------|-------|

| Name                              | Description            | End Node | Middle Node | Units |

| R <sub>TA</sub> , R <sub>TB</sub> | Termination Resistors  | 47       | 24          | Ω     |

| C1                                | Capacitor              | 4700     | 4.7         | pF    |

| R1                                | Resistor               | -        | 47          | Ω     |

| C <sub>TA</sub> , C <sub>TB</sub> | Termination Capacitors | -        | 100         | pF    |

#### **Common Mode Choke**

A common mode choke is used to improve the emission and immunity performance. The function of the common mode choke is to force the current in both signal wires to be of the same strength, but opposite direction. Therefore, the choke represents high impedance for common mode signals. The parasitic stray inductance should be as low as possible in order to keep oscillations on the bus low. The common mode choke is placed between transceiver and split termination [2].

Figure 10. ECU with Split Termination and Common Mode Choke [2]

Table 8. COMMON MODE CHOKE REQUIREMENTS [2]

| Name             | Description         | Тур   | Units |

|------------------|---------------------|-------|-------|

| R <sub>CMC</sub> | Resistance per Line | ≤1    | Ω     |

| L <sub>CMC</sub> | Main Inductance     | ≥ 100 | μΗ    |

| $L_\sigma$       | Stray Inductance    | <1    | μΗ    |

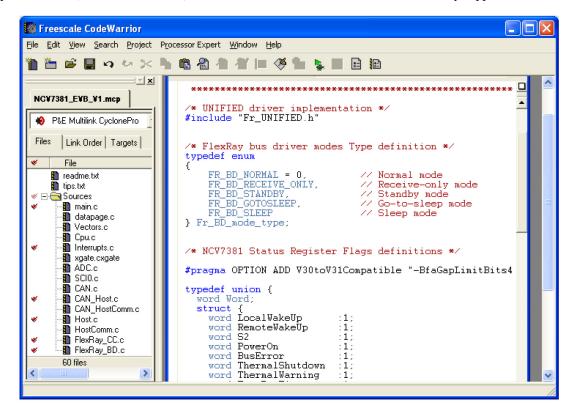

#### MCU PROGRAMMING INTERFACE

The NCV7381 EVB firmware can be freely reprogrammed using MCU programming and debugging interface (J10). The used Freescale MC9S12XF Family MCU can be programmed with P&E USB Multilink BDM module.

#### **P&E USB Multilink BDM Module Distributors**

| Distributor          | Telephone      | Email                            |

|----------------------|----------------|----------------------------------|

| Arrow Electronics    | (877) 237–8621 | onlinesales@arrow.com            |

| Avnet Electronics    | (800) 408–8353 | customer.care@avnet.com          |

| Digi-Key Corporation | (800) 344–4539 | webmaster@digikey.com            |

| Future Electronics   | (800) 675–1619 | e_services@FutureElectronics.com |

| Mouser Electronics   | (800) 346–6873 | sales@mouser.com                 |

| Newark               | (800) 463–9275 | sales@newarkinone.com            |

#### **Software Development Tool**

Suitable development tool allowing programming and debugging Freescale microcontrollers is CodeWarrior™ Development Studio (www.freescale.com). The P&E USB Multilink BDM module is directly supported.

The NCV7381 EVB firmware can be downloaded from ON Semiconductor web site (www.onsemi.com).

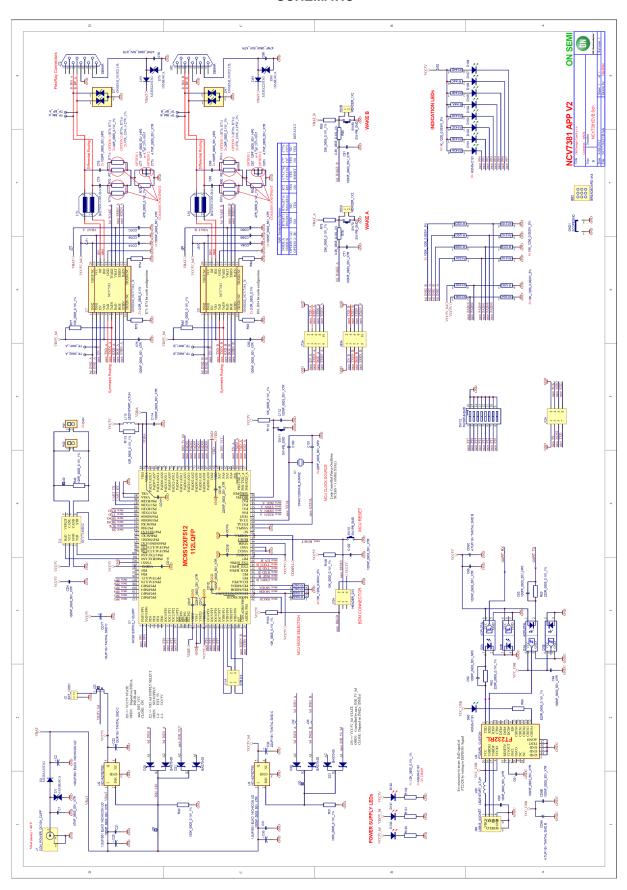

#### **SCHEMATIC**

#### **PCB DRAWINGS**

#### **Assembly Drawings**

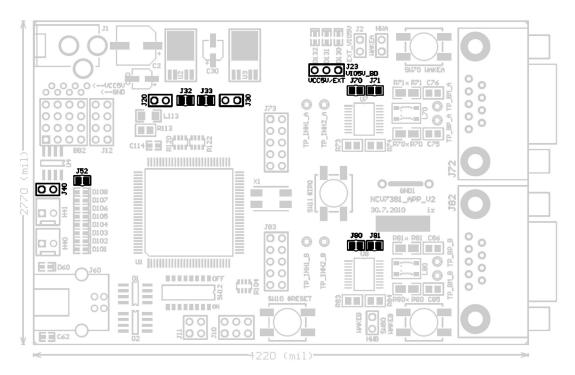

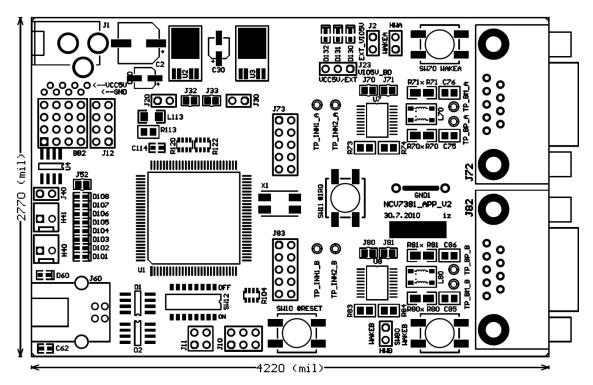

Figure 11. NCV7381 EVB PCB Top Assembly Drawing

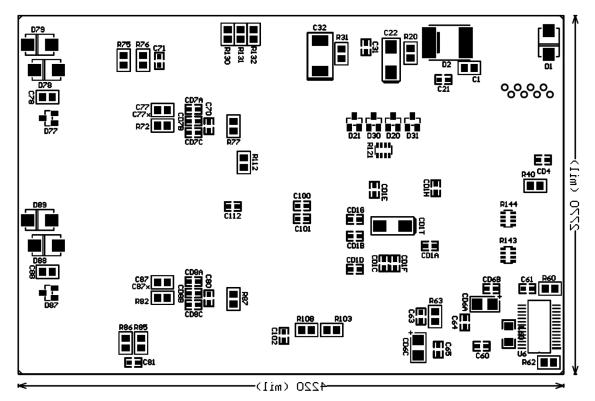

Figure 12. NCV7381 EVB PCB Bottom Assembly Drawing

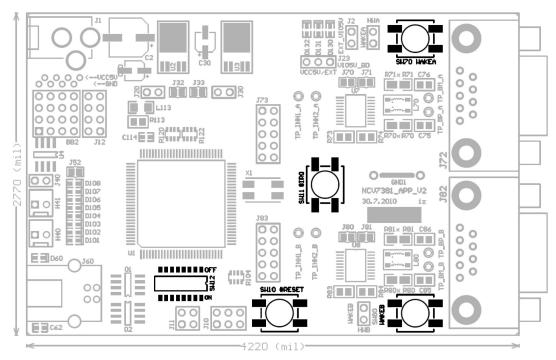

## **Composite Drawings**

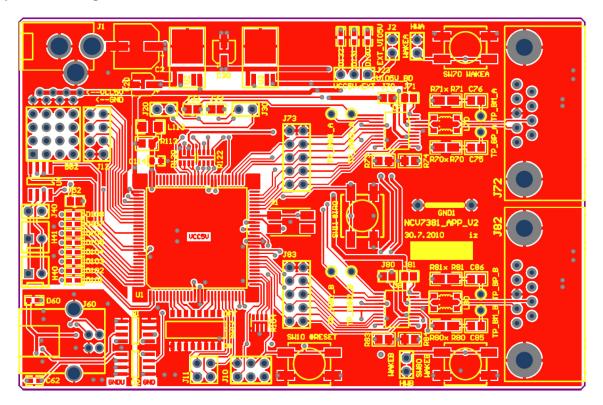

Figure 13. NCV7381 EVB PCB Top Composite Drawing

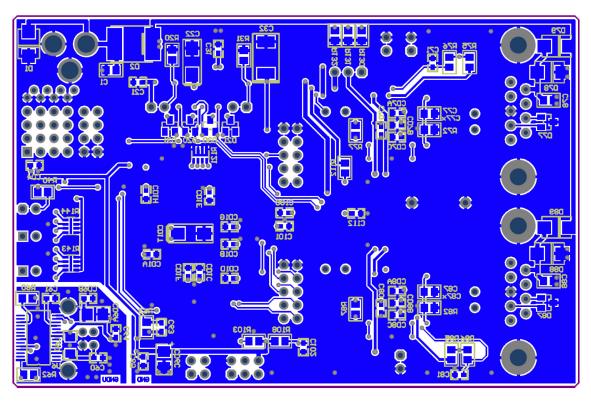

Figure 14. NCV7381 EVB PCB Bottom Composite Drawing (Mirrored)

#### **PCB General Parameters**

• Material: FR4

• Cu Plating Thickness: 18 μm 0.5 oz

• Surface Treatment: Au

• Solder Resist: Green, Both Sides

#### **Dimensions**

Length: 107.2 mm 4220 mil

Width: 70.4 m 2770 mil

• Thickness: 1.5 mm

• Minimum Clearance: 0.25 mm 9.842 mil

#### **REFERENCES**

- On Semiconductor, NCV7381 FlexRay<sup>®</sup> Transceiver, Rev. 0, May 2012.

FlexRay Consortium. FlexRay Communications System Electrical Physical Layer Specification, V3.0.1, October 2010.

FlexRay Consortium. FlexRay Communications System Physical Layer EMC Measurement Specification, V3.0.1, October 2010.

#### PACKAGE DRAWING AND DIMENSIONS

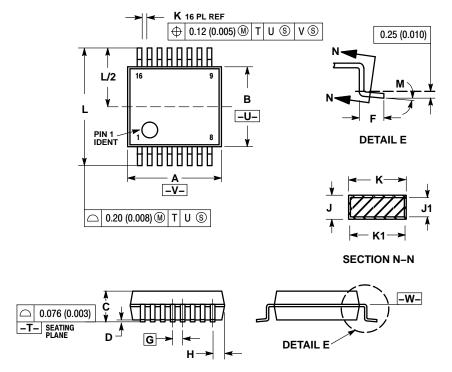

16 LEAD SSOP CASE 940B-03 ISSUE D

SCALE 2:1

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI

Y14 5M 1982

- 2. CONTROLLING DIMENSION: MILLIMETER.

- 3. DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- (U.006) FER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

- 5. DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION/INTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF K DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR INTRUSION SHALL NOT REDUCE DIMENSION K BY MORE THAN 0.07 (0.002) AT LEAST MATERIAL CONDITION

- 6. TERMINAL NUMBERS ARE SHOWN FOR

- REFERENCE ONLY.

7. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE -W-.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 6.07        | 6.33 | 0.238     | 0.249 |

| В   | 5.20        | 5.38 | 0.205     | 0.212 |

| С   | 1.73        | 1.99 | 0.068     | 0.078 |

| D   | 0.05        | 0.21 | 0.002     | 0.008 |

| F   | 0.63        | 0.95 | 0.024     | 0.037 |

| G   | 0.65 BSC    |      | 0.026 BSC |       |

| Н   | 0.73        | 0.90 | 0.028     | 0.035 |

| J   | 0.09        | 0.20 | 0.003     | 0.008 |

| J1  | 0.09        | 0.16 | 0.003     | 0.006 |

| K   | 0.25        | 0.38 | 0.010     | 0.015 |

| K1  | 0.25        | 0.33 | 0.010     | 0.013 |

| L   | 7.65        | 7.90 | 0.301     | 0.311 |

| M   | 0 °         | 8 °  | 0 °       | 8 °   |

FlexRay is a registered trademark of FlexRay Consortium. Freescale is a trademark of Freescale Semiconductor, Inc.

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opport

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative