# Synchronous FET Controller

## HIGH RELIABILITY PRODUCTS

#### Features

- Current-sense control for low or high-side synchronous rectifiers

- Rectifier turn on/off thresholds set with external resistors

- Minimum ON and OFF time to minimize GATE turnon oscillation

- Wide supply range 8V to 24V

- Gate drive internally limited to 10V

- 2A sink, 1A source gate drive

- 4mm x 5mm SOIC-8 package

- Product is lead-free, Halogen Free, RoHS / WEEE compliant

- Military temperature range

#### **Applications**

- LLC converters

- Flyback converters

### Description

TS4305BM is a synchronous rectifier controller for AC-DC power supply's secondary side rectification.

#### **Specifications**

- Drives low or high side N-channel MOSFET

- Sync-FET control based on current sensing in low or high-side sense resistor

- -55°C to +125°C T<sub>J</sub> operation

- Operation to 24V

- 2A/1A sink/source gate drive

- 10V gate drive capability

- 100ns propagation delay between current sense to GATE drive

- 180µA (typical) quiescent current in low power mode

- Under voltage lock out protection

- Over temperature shut down (TSD) protection

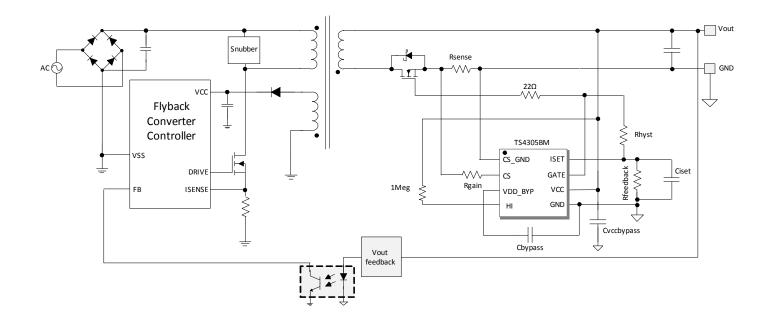

## **Typical Application Circuit**

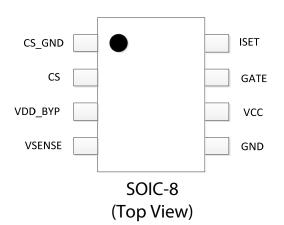

## **Pin Configuration**

## **Pin Configuration**

| SOIC-8 Pin # | Pin Name | Function             | Description                                          |

|--------------|----------|----------------------|------------------------------------------------------|

| 1            | CS_GND   | Current Sense        | Current sense resistor high-side terminal            |

| 2            | CS       | Current Sense        | Current sense resistor low-side terminal             |

| 3            | VDD_BYP  | Power Bypass         | External bypass capacitor for internal 5V VDD supply |

| 4            | Н        | Vendor Test Mode     | Tie to VCC through 1Meg resistor                     |

| 5            | GND      | Ground               | Circuit Common                                       |

| 6            | VCC      | Power Input          | Supply voltage                                       |

| 7            | GATE     | FET Gate Drive       | Gate drive, regulated voltage swing                  |

| 8            | ISET     | Current Sense Output | Current sense in voltage form using Rfeedback        |

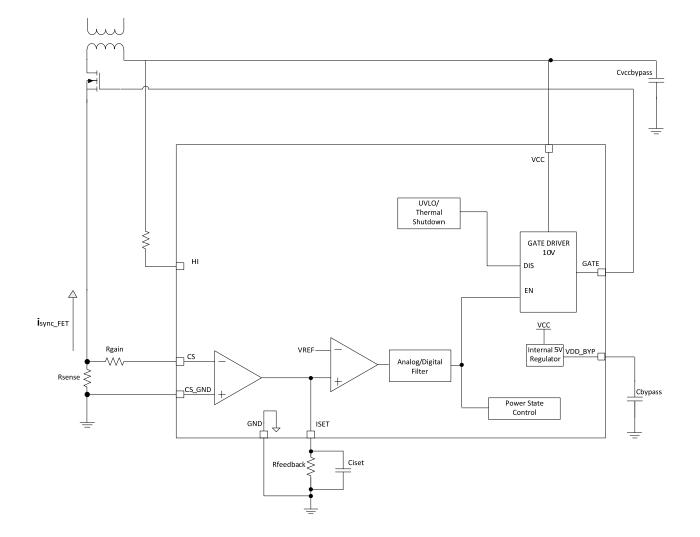

## **Functional Block Diagram**

Functional Diagram Configured in QR Flyback application

## **Absolute Maximum Ratings**

Over operating free-air temperature range unless otherwise noted (1, 2)

| Parameter                                            | Value       | Unit |

|------------------------------------------------------|-------------|------|

| VCC                                                  | -0.3 to 26  | V    |

| GATE                                                 | -0.3 to 12  | V    |

| ISET, CS, HI, VDD_BYP                                | -0.3 to 5.5 | V    |

| Electrostatic Discharge – Human Body Model           | +/-2k       | V    |

| Electrostatic Discharge – Charge Device Model        | +/-500      | V    |

| Reflow or solder Temperature (soldering, 10 seconds) | 260         | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to GND.

## **Thermal Characteristics SOIC-8**

| Symbol             | Parameter                              | Value      | Unit |

|--------------------|----------------------------------------|------------|------|

| θ <sub>JA</sub>    | Thermal Resistance Junction to Air (1) | 153        | °C/W |

| T <sub>STG</sub>   | Storage Temperature Range              | -65 to 150 | °C   |

| T <sub>J MAX</sub> | Maximum Junction Temperature           | 150        | °C   |

| ΤJ                 | Operating Junction Temperature Range   | -55 to 125 | °C   |

(1) Assumes 8LD SOIC mounted on a 1-layer FR4 2S2P JEDEC board as per JESD51-7 with 13.5 inch<sup>2</sup> of 1 oz Cu.

### **Recommended Operating Conditions**

| Symbol              | Parameter                                                | Min | Тур | Мах | Unit |

|---------------------|----------------------------------------------------------|-----|-----|-----|------|

| VCC                 | Input Operating Voltage                                  | 8   |     | 24  | V    |

| CS <sub>dv/dt</sub> | CS Input Slew Rate                                       |     |     | 10  | V/ms |

| CS <sub>Input</sub> | CS Input voltage with respect to GND                     |     |     | 100 | mV   |

| Сиссвур1            | VCC Bypass Capacitor, appropriate voltage rating per VCC |     | 10  |     | μF   |

| Cvccbyp2            | VCC Bypass Capacitor, appropriate voltage rating per VCC |     | 10  |     | pF   |

| Cbyp                | Internal 5V VDD Bypass Capacitor                         |     | 1   |     | μF   |

| F <sub>switch</sub> | Maximum Gate Drive Switching Frequency                   |     |     | 150 | kHz  |

## **Electrical Characteristics**

$T_J = 25^{\circ}C$  for typical,  $T_J = -55^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted

| Symbol                        | Parameter                                   | Condition                                                                                    | Min   | Тур | Мах  | Unit |

|-------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------|-------|-----|------|------|

| Current Sen                   | se Amplifier                                |                                                                                              |       |     | •    |      |

|                               |                                             | Tj=0°C to +85°C                                                                              | 1.99  | 2   | 2.01 | V    |

| VREF                          | 2.0V Comparator reference                   | Tj=-55°C to +125°C                                                                           | 1.965 | 2   | 2.05 | V    |

| Supply                        |                                             |                                                                                              |       |     |      |      |

| VCC                           | Supply voltage                              |                                                                                              | 8     |     | 24   | V    |

| I <sub>supply</sub>           | Quiescent supply current                    | CS amp = Off during lockout time period                                                      |       | 180 | 300  | μA   |

| VLGC                          | Internal LV supply for logic                |                                                                                              |       | 5   |      | V    |

| T <sub>SD</sub>               | Thermal shutdown temperature <sup>(1)</sup> |                                                                                              |       | 135 |      | °C   |

| Under Volta                   | age Lock Out                                |                                                                                              |       |     |      |      |

| $V_{\text{UVLO}\_\text{ON}}$  | UV Turn On Threshold (VCC)                  | 10V Gate Drive                                                                               | 8     | 9   | 10   | v    |

| $V_{\text{UVLO}\_\text{OFF}}$ | UV Turn Off Threshold (VCC)                 | 10V Gate Drive                                                                               | 7.5   | 8.5 | 9.5  | V    |

| $V_{\text{UVLO\_hyst}}$       | UVLO hysteresis                             | 10V Gate Drive                                                                               | 0.35  |     | 1.0  | V    |

| Gate Drive                    |                                             | L                                                                                            |       | L   |      |      |

| V <sub>GATE</sub>             | Gate drive voltage                          | 10V Gate Drive, VCC > 13V                                                                    | 7.75  | 10  | 13   | V    |

| R <sub>DRVHI</sub>            | Gate drive source resistance                | VCC>13V, Gate=10V, T_=25°C, IL=50mA                                                          |       | 7.2 | 17   | Ω    |

| R <sub>DRVLO</sub>            | Gate drive sink resistance                  | VCC>13V, Gate=10V, T_=25°C                                                                   |       | 2.1 | 3.1  | Ω    |

| $t_{\text{prop}\_dly}$        | Propagation delay from CS to<br>GATE        | -20mV step, $R_{sense}$ =5m $\Omega$ , $R_{gain}$ =5 $\Omega$ , $R_{feedback}$ =10k $\Omega$ |       | 53  |      | ns   |

| Ton_pulse                     | Minimum gate ON pulse width                 |                                                                                              | 0.8   | 1.3 | 1.8  | μs   |

| Toffblanking                  | Minimum gate OFF blanking width             |                                                                                              | 1.0   | 2.3 | 4.6  | μs   |

(1) Not tested in production

#### **Detailed Description of Operation**

TS4305BM is intended for use on the secondary side of a power supply to drive a synchronous MOSFET. Unlike traditional synchronous MOSFET controllers, the TS4305BM uses an architecture that synchronizes the rectification FET with the secondary-side current as opposed to the secondary side voltage. Because secondary side current and voltage are not necessarily in phase, the zero current detection method yields to a more efficient operation as opposed to operation with voltage detection only.

#### Synchronous Rectifier Control

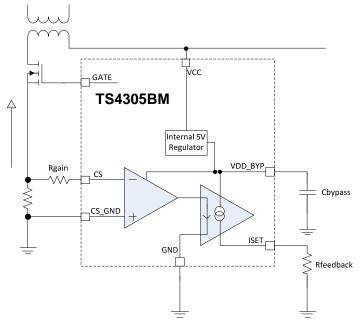

The TS4305BM uses a current mirror in conjunction with a high-sensitivity, low-offset voltage op-amp specifically designed for sensing voltages near the low-side supply rail. This op-amp operates over a small range of input voltage suited specifically for converting the voltage across a low-ohmic sense resistor to current. The equivalent circuit is shown below with typical values for external components:

In the above figure, the syncFET current flows through an external  $5m\Omega$ . There is also an external gain resistor Rgain =  $5\Omega$  and a feedback resistor Rfeedback =  $10k\Omega$ . The amplifier inside the TS4305BM holds the voltage at the CS pin close to the GND pin over a small operating range in which  $i_{sync\_FET}$  is positive. Over this operating range, the voltage at ISET will be equal to  $(i_{sync\_FET}x5m\Omega)x(10k\Omega/5\Omega)$ .

TS4305BM contains a comparator that compares the voltage at ISET to an internal reference which is set to 2.0V at  $T_J=25$ °C. In the example shown above, when VREF = 2V, the current trip level would be 200mA. This level can be adjusted by changing Rsense, Rgain, and Rfeedback.

A hysteresis resistor can also be connected between the gate drive output and ISET to provide hysteresis in the ON/OFF trip values. In this case, the gate turn on is expected when  $I_{sync_{FET}}$  is greater than:

$$Isync_{FETon} \gtrsim \frac{2 * Rgain}{(Rfeedback || Rhysteresis) * Rsense}$$

Using the example values Rgain = 5 $\Omega$ , Rsense=5m $\Omega$ , Rfeedback = 10k $\Omega$ , Rhysteresis=100k $\Omega$ , Isync<sub>FETon</sub>  $\gtrsim 220mA$ .

The gate will turn off when I<sub>sync\_FET</sub> falls below the level according to:

$$Isync_{FEToff} \lesssim \frac{\left[ \left( \frac{2.0}{Rfeedback} - \frac{Vgate - 2.0}{Rhysteresis} \right) * Rgain \right]}{Rsense}$$

Which yields  $Isync_{FEToff} \leq 120 mA$  using the same example values with the Vgate=10V gate drive option.

If the signal frequency on the ISET pin is above approximately 200kHz at 27°C (~150kHz at -40°C and ~300kHz at 125°C), the gate driver output will latch low to prevent the synchronous FET from operating. This condition is maintained until VCC is power cycled.

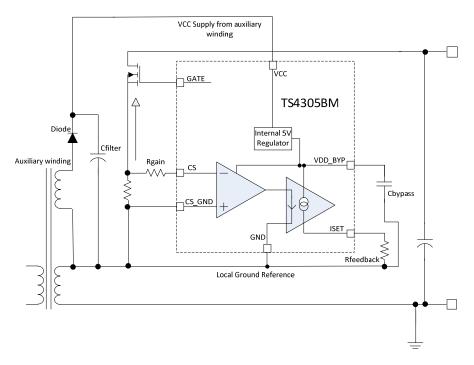

TS4305BM can also be configured for sensing voltages on the high-side supply rail. One possible implementation can be accomplished by powering TS4305BM through an auxiliary winding and diode-capacitor filter as shown below. Alternative charge pump schemes can also be contemplated.

High-side Rectification with auxiliary winding and diode-capacitor filter to power TS4305BM

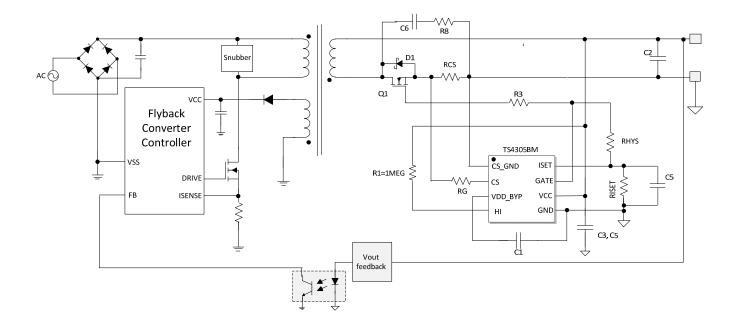

# **Application Schematic**

| Component | Schematic | Notes                                    |  |

|-----------|-----------|------------------------------------------|--|

|           | Value     |                                          |  |

| R1        | 1MegΩ     | HI pin tie off to VCC                    |  |

| R3        | 2Ω        | Gate resistor                            |  |

| R8        | 10Ω       | Snubber resistor, sized for proper power |  |

| RCS       | 5mΩ       | Sense resistor                           |  |

| RG        | 5.1Ω      | Rgain resistor                           |  |

| RISET     | 10kΩ      | lset resistor                            |  |

| RHYS      | 100kΩ     | Hysteresis resistor                      |  |

| C1        | 1μF       | Internal 5V filter capacitor             |  |

| C2        | 10µF      | 25V VCC filter capacitor                 |  |

| C3        | 22pF      | 25V VCC filter capacitor                 |  |

| C5        | 10µF      | 25V VCC filter capacitor                 |  |

| C6        | 1nF       | Snubber capacitor, rated for proper Vds  |  |

| Q1        |           | Power NMOS, with proper Vds rating       |  |

| D1        |           | 100V schottky diode                      |  |

| U1        |           | TS4305BM SOIC, 10V Gate Drive            |  |

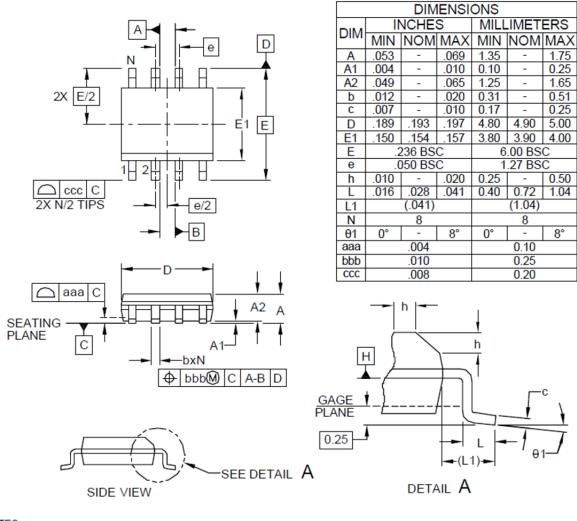

#### Package Drawing: SOIC-8

NOTES:

- 1. CONTROLLING DIMENSIONS ARE IN MILLIMETERS (ANGLES IN DEGREES).

- 2. DATUMS -A- AND -B- TO BE DETERMINED AT DATUM PLANE -H-

- 3. DIMENSIONS "E1" AND "D" DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 4. REFERENCE JEDEC STD MS-012, VARIATION AA.

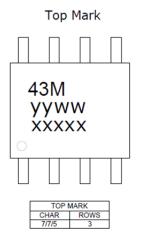

#### Package Marking: SOIC-8

Marking for the SOIC 8 Lead package: nnnnn = Part Number (Example: 43M) yyww = Date code (Example: 1752) xxxxx = Semtech Lot No. (Example: E9010)

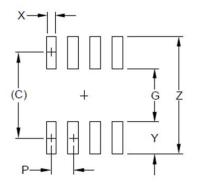

#### Landing Pattern: SOIC-8

| DIMENSIONS            |            |        |  |  |

|-----------------------|------------|--------|--|--|

| DIM INCHES MILLIMETER |            |        |  |  |

| С                     | (.205)     | (5.20) |  |  |

| G                     | G .118 3.0 |        |  |  |

| P                     | .050       | 1.27   |  |  |

| X                     | .024       | 0.60   |  |  |

| Y                     | .087       | 2.20   |  |  |

| Z                     | .291       | 7.40   |  |  |

NOTES:

- 1. THIS LAND PATTERN IS FOR REFERENCE PURPOSES ONLY. CONSULT YOUR MANUFACTURING GROUP TO ENSURE YOUR COMPANY'S MANUFACTURING GUIDELINES ARE MET.

- 2. REFERENCE IPC-SM-782A, RLP NO. 300A.

#### **Ordering Information**

| Device Part Number | Description                             | Package                                  |

|--------------------|-----------------------------------------|------------------------------------------|

| TS4305BMSTRT       | 10V Gate Drive, 8ms lockout period      | SOIC-8<br>Tape & Reel (2,500 parts/reel) |

| TS4305BEVB         | TS4305B evaluation board <sup>(1)</sup> |                                          |

(1) The evaluation board is populated with industrial temperature grade device

#### **IMPORTANT NOTICE**

Information relating to this product and the application or design described herein is believed to be reliable, however such information is provided as a guide only and Semtech assumes no liability for any errors in this document, or for the application or design described herein. Semtech reserves the right to make changes to the product or this document at any time without notice. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. Semtech warrants performance of its products to the specifications applicable at the time of sale, and all sales are made in accordance with Semtech's standard terms and conditions of sale.

SEMTECH PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS, OR IN NUCLEAR APPLICATIONS IN WHICH THE FAILURE COULD BE REASONABLY EXPECTED TO RESULT IN PERSONAL INJURY, LOSS OF LIFE OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. INCLUSION OF SEMTECH PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE UNDERTAKEN SOLELY AT THE CUSTOMER'S OWN RISK. Should a customer purchase or use Semtech products for any such unauthorized application, the customer shall indemnify and hold Semtech and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs damages and attorney fees which could arise.

The Semtech name and logo are registered trademarks of the Semtech Corporation. All other trademarks and trade names mentioned may be marks and names of Semtech or their respective companies. Semtech reserves the right to make changes to, or discontinue any products described in this document without further notice. Semtech makes no warranty, representation or guarantee, express or implied, regarding the suitability of its products for any particular purpose. All rights reserved.

© Semtech 2017

#### **Contact Information**

Semtech Corporation 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111, Fax: (805) 498-3804 www.semtech.com