# Hardware Reference Manual

**REV. November 2020**

## **SandCat**

(VL-EPM-39)

Intel® Atom<sup>™</sup>-based Single Board Computer with Ethernet, Video, USB, SATA, Serial I/O, Digital I/O, Counter/Timers, Mini PCle, mSATA and PCI/104-*Plus* Interface.

#### WWW.VERSALOGIC.COM

12100 SW Tualatin Road Tualatin, OR 97062-7341 (503) 747-2261 Fax (971) 224-4708

Copyright © 2018-2020 VersaLogic Corp. All rights reserved.

#### Notice:

Although every effort has been made to ensure this document is error-free, VersaLogic makes no representations or warranties with respect to this product and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose.

VersaLogic reserves the right to revise this product and associated documentation at any time without obligation to notify anyone of such changes.

PC/104 and the PC/104 logo are trademarks of the PC/104 Consortium.

\* Other names and brands may be claimed as the property of others.

### **Product Release Notes**

| Release 1.0               | October 2018                                                           | Initial Release                                                  |

|---------------------------|------------------------------------------------------------------------|------------------------------------------------------------------|

| Release 1.1               | April 2019                                                             | Added I <sup>2</sup> C pinouts to table 7                        |

| Release 1.2               | Release 1.2 May 2020 Removed link to OS compatibility chart on page 12 |                                                                  |

| Release 1.3 November 2020 |                                                                        | Updated power setup (page 8) Updated CBR-4005B image (figure 21) |

### **Cautions**

#### **ELECTROSTATIC DISCHARGE**

Electrostatic discharge (ESD) can damage boards, disk drives and other components. The circuit board must only be handled at an ESD workstation. If an approved station is not available, some measure of protection can be provided by wearing a grounded antistatic wrist strap. Keep all plastic away from the board, and do not slide the board over any surface.

After removing the board from its protective wrapper, place the board on a grounded, static-free surface, component side up. Use an antistatic foam pad if available.

The board should also be protected inside a closed metallic anti-static envelope during shipment or storage.

#### **MOUNTING SUPPORT**

The single board computer must be supported at all four mounting points to prevent excessive flexing when expansion modules are attached and removed. Flex damage caused by excessive force on an improperly mounted circuit board is not covered under the product warranty.

#### **EARTH GROUND REQUIREMENT**

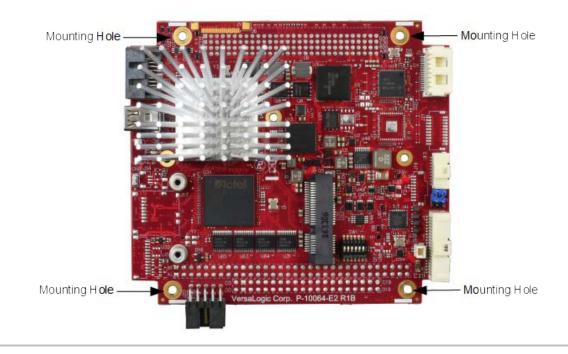

All mounting standoffs should be connected to earth ground (chassis ground). This provides proper grounding for EMI purposes. The figure below shows the location of the board's mounting holes. All mounting holes identified in the figure must be connected to earth ground.

Figure 1. Attaching the EPM-39 to Earth Ground

## **Contents**

| Introduction                                   | 1  |

|------------------------------------------------|----|

| Description                                    | 1  |

| Technical Specifications                       | 3  |

| Thermal Considerations                         | 3  |

| EPM-39 Block Diagram                           | 4  |

| Dimensions and Mounting                        |    |

| Hardware Assembly                              | 6  |

| Related Documents                              | 6  |

| Configuration and Setup                        | 7  |

| Initial Configuration                          |    |

| Basic Setup                                    | 7  |

| Jumper Blocks                                  |    |

| Jumpers Blocks in the As-Shipped Configuration | 10 |

| Jumper Summary                                 | 10 |

| Configuration Switches                         |    |

| Resetting the BIOS to Factory Defaults         | 12 |

| Clearing Non-volatile RAM and RTC Registers    |    |

| BIOS Setup Utility                             |    |

| Operating System Installation                  | 13 |

| Board Features                                 | 14 |

| CPU                                            |    |

| System RAM                                     |    |

| I/O Interfaces                                 |    |

| Power Delivery                                 |    |

| Main Power Connector                           |    |

| Cabling                                        |    |

| Power Delivery Considerations                  |    |

| Power Button                                   |    |

| Supported Power States                         |    |

| Battery Power Options                          |    |

| Cabling                                        |    |

| VL-CBR-0203 External Battery Module            |    |

| Real Time Clock (RTC)                          | 19 |

| Push-Button Reset                              | 19 |

| LEDs/Indicators                                | 20 |

| Programmable LED                               | 20 |

| Power LEDs                                     |    |

| External Speaker                               | 21 |

| Mass Storage Interfaces                        | 22 |

| SATA                                           |    |

| Multi-nurnoso I/O                              | 22 |

| USB Interfaces                                                   | 23 |

|------------------------------------------------------------------|----|

| PCIe Mini Card / mSATA                                           | 23 |

| mSATA Activity LED                                               | 25 |

| PCIe Mini Card LEDs                                              |    |

| User I/O Connector                                               |    |

| Cabling                                                          |    |

| Serial Ports                                                     |    |

| Serial Port Connectors                                           |    |

| Serial Port Connector Pinouts                                    |    |

|                                                                  |    |

| CablingRS-485 Mode Line Driver Control                           |    |

|                                                                  |    |

| Video Interfaces                                                 |    |

| Mini DisplayPort Connector                                       |    |

| Console Redirection                                              | 33 |

| Network Interfaces                                               | 34 |

| Ethernet Connector                                               |    |

| Cabling                                                          | 35 |

| On-Board Ethernet Status LEDs                                    |    |

| Expansion Interfaces                                             | 37 |

| PC/104-Plus Expansion Bus                                        |    |

| ISA Bus (on PC/104- <i>Plus</i> and PC/104 Expansion Modules)    |    |

| ISA I/O Support                                                  |    |

| ISA Memory Support                                               |    |

| ISA IRQ Support                                                  |    |

| - **                                                             |    |

| Each of the IRQs must be enabled in the BIOS Setup utility befor | •  |

| used. (All are disabled by default.)                             |    |

| PCI Bus (on PC/104-Plus and PCI-104 Expansion Modules)           |    |

| System Resources and Maps                                        | 40 |

| CBR-4005B Paddleboard                                            | 41 |

| CBR-4005B Paddleboard                                            | 41 |

| CBR-4005B Connectors and Indicators                              |    |

| User I/O Connector                                               |    |

| Cabling                                                          |    |

| On-board Battery                                                 |    |

| Auxiliary I/O Connector                                          |    |

| Dimensions and Mounting Holes                                    |    |

| _                                                                |    |

| Thermal Considerations                                           |    |

| The Thermal Solution for Your Application                        |    |

| Heat Sink                                                        |    |

| General System-level Considerations                              |    |

| CPU Thermal Trip Points                                          |    |

| Thermal Specifications, Restrictions, and Conditions             |    |

| Overall Restrictions and Conditions                              |    |

| Heat Sink Considerations:                                        |    |

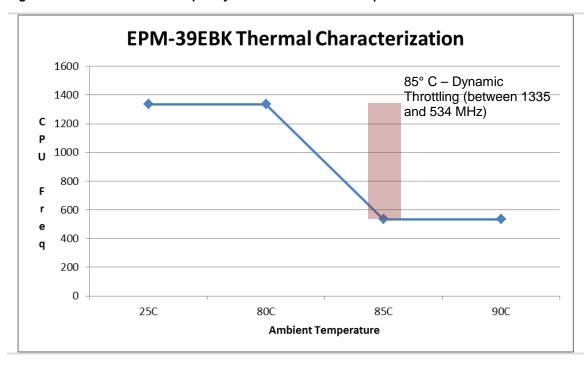

| FPM-39 Thermal Characterization                                  | 50 |

| Test Results                                                                                                | 51            |

|-------------------------------------------------------------------------------------------------------------|---------------|

|                                                                                                             | Figures       |

| Figure 1. Attaching the EPM-39 to Earth Ground                                                              | iv            |

| Figure 2. VL-EPM-39 Single Board Computer (Top Side)                                                        |               |

| Figure 3. VL-EPM-39 Single Board Computer (Bottom Side).                                                    |               |

| Figure 4. EPM-39 Dimensions and Mounting Holes                                                              |               |

| Figure 5. Jumper Block Locations                                                                            | 10            |

| Figure 6. Location of SW1 Configuration Switch Block                                                        | 11            |

| Figure 7. Location and Pin Orientation of the Main Power Con                                                |               |

| Figure 8. Location and Pin Orientation of the External Battery                                              |               |

| Figure 9. VL-CBR-0203 Latching Battery Module                                                               |               |

| Figure 10. Locations of the LEDs/Indicators                                                                 |               |

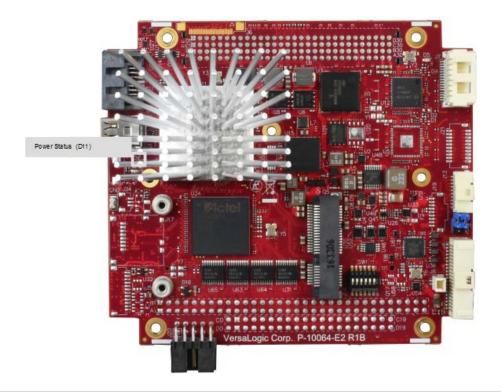

| Figure 11. Location of the D11 Dual-color LED                                                               |               |

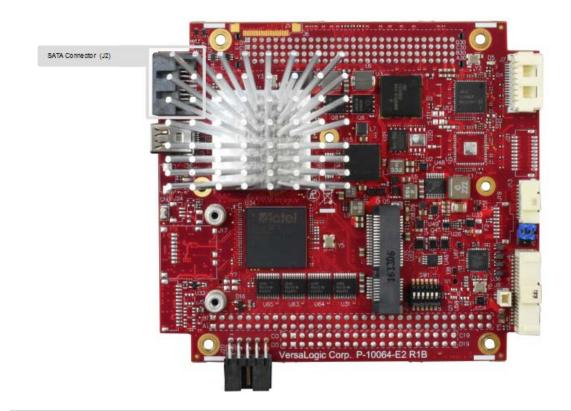

| Figure 12. Location of the SATA Port                                                                        |               |

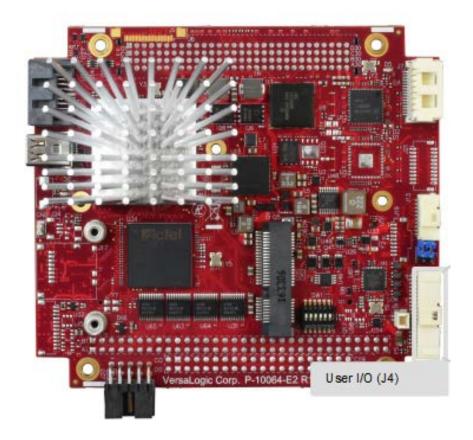

| Figure 13. Location of the User I/O to VL-CBR-4005B                                                         |               |

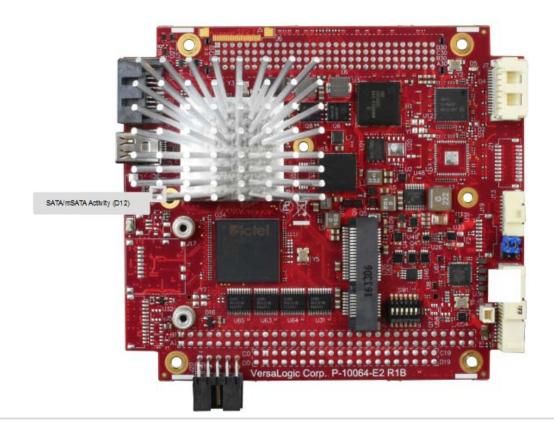

| Figure 14. Location of the SATA/mSATA Activity LED                                                          |               |

| Figure 15. Location of PCIe Mini Card LEDs<br>Figure 16. Location and Pin Orientation of User I/O Connector |               |

| Figure 17. Location and Pin Orientation of Serial Port Connect                                              |               |

| Figure 18. Location of the Mini DisplayPort Connector                                                       |               |

| Figure 19. Location and Pin Orientation for the J7 Ethernet Co                                              |               |

| Figure 20. Location of Ethernet Status LED                                                                  |               |

| Figure 21. CBR-4005B Connectors, Switches, and LEDs                                                         |               |

| Figure 22. Location and Pin Orientation of the User I/O Conne                                               |               |

| Figure 23. Location and Pin Orientation of Auxiliary I/O Conn                                               |               |

| Figure 24. CBR-4005B Dimensions and Mounting Holes                                                          |               |

| Figure 25. EPM-39EBK CPU Frequency Relative to Ambient                                                      | Temperature51 |

|                                                                                                             |               |

|                                                                                                             | Tobloo        |

|                                                                                                             | Tables        |

| Table 1: Jumper Summary                                                                                     |               |

| Table 2: Switch Setting Summary                                                                             |               |

| Table 3: J20 Main Power Connector Pinout                                                                    |               |

| Table 4: Supported Power States                                                                             | 17            |

| Table 5: PCIe Mini Card / mSATA Pinout                                                                      |               |

| Table 6: PCIe Mini Card LED States                                                                          |               |

| Table 7: J4 I/O Connector Pinout and Pin Orientation                                                        |               |

| Table 8: J13 COM1/COM2 Connector Pinout                                                                     |               |

| Table 9: J3 Mini DisplayPort Connector Pinout                                                               |               |

| Table 10: Ethernet Connector Pinout                                                                         | 35            |

| Table 11: Ethernet Status LEDs                         | 36 |

|--------------------------------------------------------|----|

| Table 12: PCI/104-Plus Connector (PCI) Maximum Current | 37 |

| Table 13: Available ISA Bus I/O Ranges                 | 38 |

| Table 14: User I/O Connector Pinout                    | 42 |

| Table 15: Auxiliary I/O Connector Pinout               | 44 |

| Table 16: CPU Thermal Trip Points                      | 48 |

| Table 17: Temperature Monitoring Programs              | 48 |

| Table 18: EPM-39 Thermal Testing Setup                 | 50 |

Introduction 1

### **Description**

The EPM-39 is a low-power / high-performance single board computer (SBC) with a traditional PC/104-Plus expansion interface. This combination makes it easy to upgrade existing systems to a powerful 4th generation Atom processor, while preserving plug-in expansion to existing specialty I/O boards. In addition, it also contains a variety of on-board I/O interfaces, including USB, a mini PCIe expansion socket, and digital I/O ports.

- Intel Atom "Bay Trail" dual-core processor, with processor clock rates up to 1.33 GHz (Atom E3825)

- Integrated Intel Gen 7 graphics core supports DirectX 11, OpenGL 4, and H.264, MPEG-2 encoding/decoding. Mini DisplayPort video output.

- Up to Eight GB DDR3L memory, one SO-DIMM socket

- Ethernet, auto-detect 10Base-T / 100Base-TX / 1000Base-T

- Four USB 2.0 ports support keyboard, mouse, and other devices.

- Two RS-232/422/485 serial ports

- Three 8254 timer/counters

- Eight digital I/O lines

- SATA port, 3 Gb/s

- Mini PCIe socket, supports Wi-Fi modems, GPS receivers, flash storage, and other modules

- PC/104 form factor with PC/104-Plus expansion

- Customization available

The EPM-39 is compatible with popular operating systems such as Microsoft Windows\*, Windows Embedded, Linux, VxWorks\*, and QNX\*.

EPM-39 boards are subjected to complete functional testing and are backed by a limited five-year warranty. Careful parts sourcing and US-based technical support ensure the highest possible quality, reliability, service, and product longevity for this exceptional single-board computer (SBC).

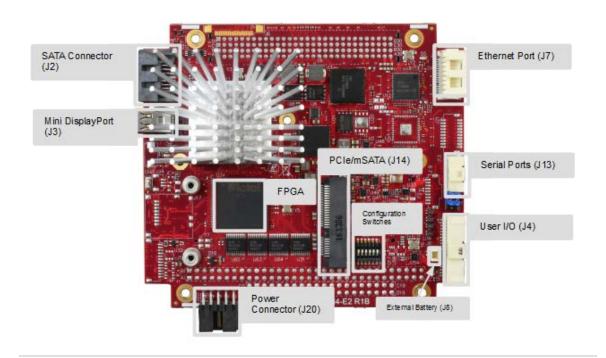

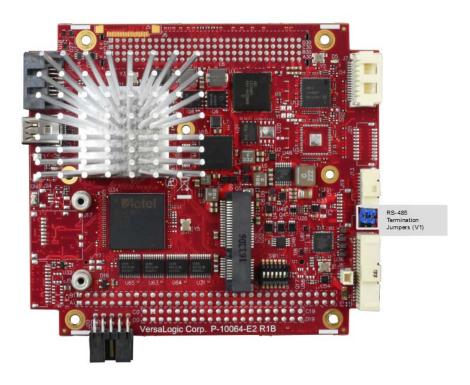

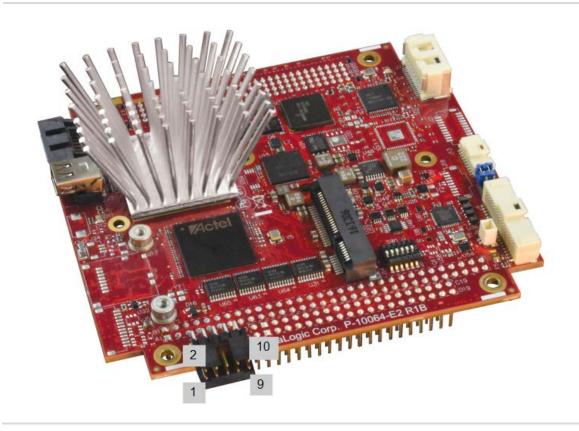

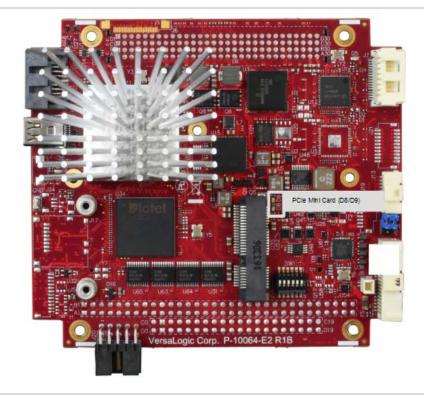

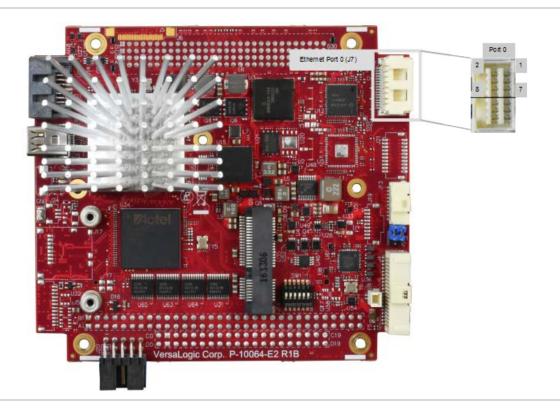

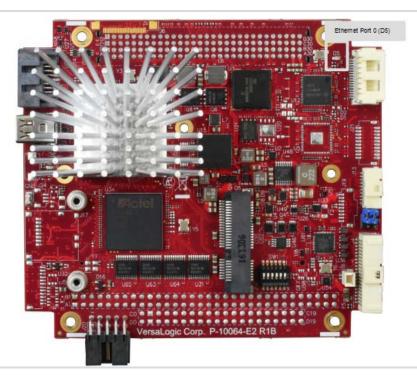

The next figure shows the connectors and major components on the top side of the board. Figure 3 shows the connectors and major components on the bottom side of the board.

Figure 2. VL-EPM-39 Single Board Computer (Top Side)

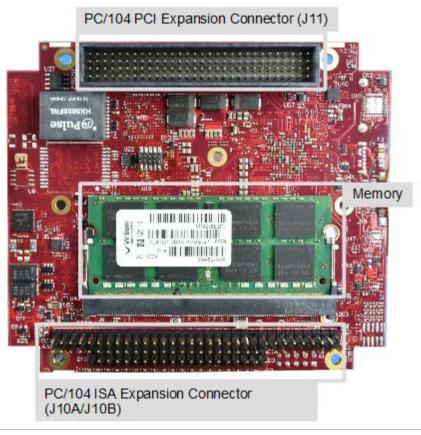

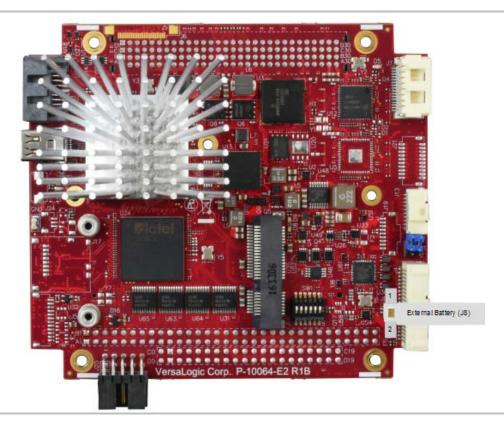

Figure 3. VL-EPM-39 Single Board Computer (Bottom Side)

## **Technical Specifications**

See the EPM-39 Data Sheet for complete specifications.

### **Thermal Considerations**

The operating temperature for the EPM-39 is -40  $^{\circ}$ C to +85  $^{\circ}$ C, de-rated -1.1  $^{\circ}$ C per 305m (1,000 ft.) above 2,300m (7,500 ft.). All SandCat models include an aluminum alloy heatsink. Refer to the Thermal Characterization section for information on additional thermal solutions.

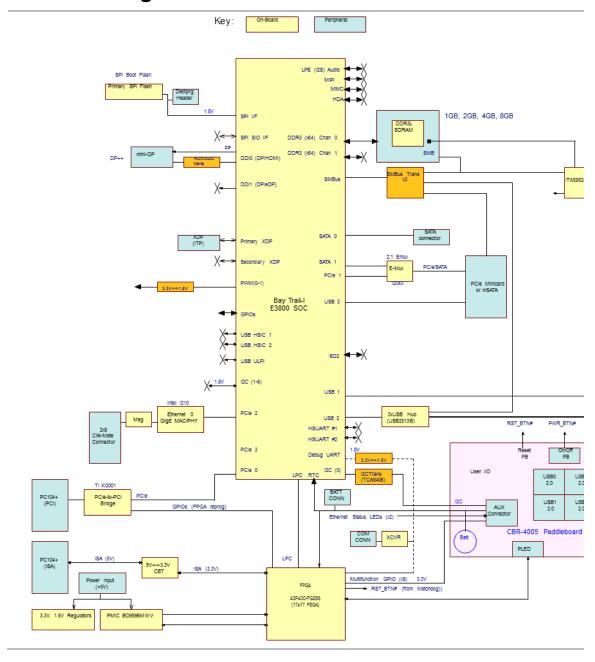

## **EPM-39 Block Diagram**

### **Dimensions and Mounting**

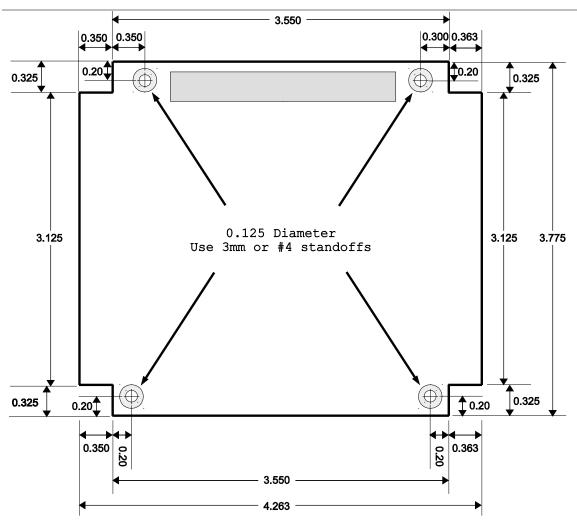

The EPM-39 complies with the PC/104 standard which provides for specific mounting hole and PC/104-*Plus* stack locations as shown below.

Figure 4. EPM-39 Dimensions and Mounting Holes

(Not to scale. All dimensions in inches.)

#### **CAUTION:**

The EPM-39 must be supported at all four mounting points to prevent excessive flexing when expansion modules are attached and removed. Flex damage caused by excessive force on an improperly mounted circuit board is not covered under the product warranty.

#### HARDWARE ASSEMBLY

The EPM-39 mounts on four hardware standoffs using the corner mounting holes. These standoffs are secured to the underside of the circuit board using pan head screws.

The entire assembly can sit on a table top or be secured to a base plate. When bolting the unit down, make sure to secure all standoffs to the mounting surface to prevent circuit board flexing.

An extractor tool is available (part number VL-HDW-203) to separate the PC/104 modules from the stack.

### **Related Documents**

The following documents available are on the EPM-39 Product Page:

- *EPM-39 Programmer's Reference Manual* provides information on the board's resources (memory, I/O, and IRQs), a description of the FPGA's registers, and programming information for the board's hardware interfaces.

- EPM-39 BIOS Reference Manual provides information on accessing and configuring settings in the BIOS Setup utility. All BIOS menus, submenus, and configuration options are described.

- VersaAPI Installation and Reference Guide describes the shared library of API calls for reading and controlling on-board devices on certain VersaLogic products.

#### Additional documents:

| Processor                                                              |                                                     |

|------------------------------------------------------------------------|-----------------------------------------------------|

| Intel Atom E38xx (formerly "Bay Trail") System-on-Chip (SoC) Processor | Intel Atom Processor E3800 Product Family Datasheet |

| Ethernet Controller                                                    |                                                     |

| Intel I210-IT Gigabit Ethernet<br>Controller                           | Intel I210-IT Datasheet                             |

| PC/104 Specification                                                   | http://www.versalogic.com/products/PC104/index.asp  |

| PC/104-Plus Specification                                              | http://www.versalogic.com/products/PC104/index.asp  |

### **Initial Configuration**

The following components are recommended for a typical development system.

- VL-EPM-39 single board computer

- VL-MM9-xxEBN DDR3 SO-DIMM module

- ATX power supply with motherboard and disk drive connectors

- VGA video monitor

- USB Keyboard

- USB Mouse

- SATA hard drive

The following VersaLogic cables and accessories are recommended.

- Mini DisplayPort to VGA cable (CBR-2032)

- User I/O cable (CBR-4005) and accompanying paddleboard Power adapter cable (CBR-1008)

- VL-CBR-0702 SATA data cable

- VL-CBR-0401 ATX to SATA power adapter

- VL-CBR-1605 12-inch single Ethernet adapter

You will also need a Windows (or other OS) installation CD/DVD and corresponding drive.

### **Basic Setup**

The following steps outline the procedure for setting up a typical development system. The EPM-39 should be handled at an ESD workstation or while wearing a grounded antistatic wrist strap.

Before you begin, unpack the EPM-39 and accessories. Verify that you received all the items you ordered. Inspect the system visually for any damage that may have occurred in shipping. Contact <a href="Support@VersaLogic.com">Support@VersaLogic.com</a> immediately if any items are damaged or missing.

Gather all the peripheral devices you plan to attach to the EPM-39 as well as their interface and power cables.

It is recommended that you attach standoffs to the board to stabilize the board and make it easier to work with.

#### 1. Install Memory

• Insert the DDR3L DRAM module into the SO-DIMM socket on the bottom side of the board and latch it into place.

#### 2. Attach Cables and Peripherals

#### Note:

The instructions below refer to connector locations by the reference designators printed on the board's silkscreen. Figure 2 and Figure 3 show the locations of all the connectors along with their reference designators.

- Plug the Mini DisplayPort to VGA cable VL-CBR-2032 into socket J3 Attach the cable to a VGA display. (Alternatively, you can attach a DisplayPort-enabled display to the Mini DisplayPort connectors at J3. The VL-EPH-V6 video adapter card converts DisplayPort output to LVDS.)

- Plug the VL-CBR-4005A paddleboard into socket J4.

- Plug a USB CD-ROM drive, USB keyboard, and USB mouse into any of the USB connectors of the CBR-4005B paddleboard.

- Plug the SATA data cable VL-CBR-0702 into socket J2. Attach a hard drive to the connector on the cable.

- Attach the SATA power adapter cable VL-CBR-0401 to the ATX power supply and SATA drive.

- Optionally, attach a LAN cable to the Ethernet connector at J7 on the EPM-39 using the VL-CBR-1605 RJ-45 adapter.

#### 3. Attach Power

Plug the power adapter cable VL-CBR-1008 into socket J20. Attach the motherboard connector of the ATX power supply to the adapter. VL-PS-ATX12-300A ATX development power supply (requires VL-CBR-2034).

#### 4. Review Configuration

Before you power up the system, double-check all the connections. Make sure all cables are oriented correctly and that adequate power will be supplied to the VL-EPM-39 and peripheral devices.

#### 5. Power On

• Turn on the ATX power supply and the video monitor. If the system is correctly configured, a video signal should be present.

#### 6. Select a Boot Drive

During startup, press <CTRL> <B> to display the boot menu. Insert the OS installation

CD in the CD-ROM drive and select to boot from the CD-ROM drive.

#### 7. Install Operating System

■ Install the operating system according to the instructions provided by the operating system manufacturer. (See Operating System Installation on page 13.)

9

## **Jumper Blocks**

#### JUMPERS BLOCKS IN THE AS-SHIPPED CONFIGURATION

Figure 5. Jumper Block Locations

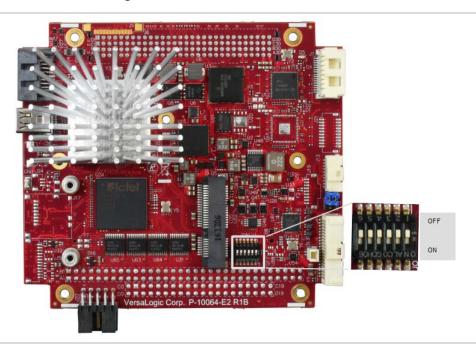

#### **JUMPER SUMMARY**

**Table 1: Jumper Summary**

| Jumper Block | Description                                    |  |

|--------------|------------------------------------------------|--|

|              | COM1 Rx End-point termination                  |  |

| V1 [1-2]     | In – COM1 terminator enabled for RS-485/RS-422 |  |

|              | Out – COM1 terminator disabled (default)       |  |

|              | COM2 Rx End-point termination                  |  |

| V1 [3-4]     | In – COM2 terminator enabled for RS-485/RS-422 |  |

|              | Out – COM2 terminator disabled (default)       |  |

## **Configuration Switches**

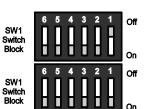

This figure shows the as-shipped switch configuration with all switches in the off position. The off position is toward the center of the board.

Figure 6. Location of SW1 Configuration Switch Block

**Table 2: Switch Setting Summary**

| SW1 Switch<br>Position | Description                                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|                        | Clears non-volatile RAM and clears resets real-time clock registers (see page 12)                                                            |

| Position 1             | Off – Normal operation (default) On – Clears battery backed up non-volatile memory bytes 0xE-0x7F and clears battery backed-up RTC registers |

|                        | No Battery Switch (see Integrator's Note below)                                                                                              |

| Position 2             | Off – A battery is being used (default) On – A battery is not being used                                                                     |

|                        | Reset BIOS to factory defaults (see page 12)                                                                                                 |

| Position 3             | Off – Normal operation (default) On – Resets BIOS to factory defaults when the board boots.                                                  |

| Position 4             | For factory use only. Always leave in the Off position.                                                                                      |

| Position 5             | SPI Flash Security – Not supported. Leave in the Off position.                                                                               |

|                        | BIOS select                                                                                                                                  |

| Position 6             | Off – Primary BIOS (default) On – Backup BIOS (optional)                                                                                     |

## \*

#### **Integrator's Note:**

- If a battery is installed (on the CBR-4005B paddleboard or externally using the J8 connector), switch position 2 must be set to the Off position. If it is set to On, the battery will discharge quickly.

- If you don't use a battery, switch position 2 should be set to the ON position. Otherwise, boot times could increase (by as much as 30 seconds in low temperature environments).

#### **RESETTING THE BIOS TO FACTORY DEFAULTS**

Reset the BIOS to default settings using the following the instructions:

1. Power off the EPM-39 and set SW1 switch position 3 to the On position (toward the outer edge of the board).

- 2. Power on the EPM-39.

- 3. After the system boots, power off the EPM-39 and set the switch back to the Off position (toward the center of the board).

4. Power on the EPM-39.

#### CLEARING NON-VOLATILE RAM AND RTC REGISTERS

Clear the non-volatile RAM and RTC registers (which includes the date/time) using the following the instructions:

- 1. Power off the EPM-39.

- 2. Set SW1 switch position 1 to the On position (toward the outer edge of the board).

3. Wait at least two seconds and set the switch back to the Off position (toward the center of the board).

4. Power on the EPM-39.

### **BIOS Setup Utility**

The EPM-39 permits users to modify the BIOS Setup utility defaults. Refer to the *EPM-39 BIOS Reference Manual* (available on the <u>EPM-39 Product Page</u>) for information on accessing and configuring settings in the BIOS Setup utility. All BIOS menus, submenus, and configuration options are described in the *EPM-39 BIOS Reference Manual*.

## **Operating System Installation**

The standard PC architecture used on the EPM-39 makes the installation and use of most of the standard x86 processor-based operating systems relatively simple. Special optimized hardware drivers for a particular operating system, or a link to the drivers, are available at the <a href="EPM-39">EPM-39</a> <a href="Product Page">Product Page</a>.

### **CPU**

The EPM-39 uses the Intel 4th Generation Atom E3825 (formerly "Bay Trail") System-on-Chip (SoC) processor:

Each core contains a 512 KB L2 cache. These processors support Intel 64-bit instructions, AES Instructions, Execute Disable Bit, and Virtualization Technology.

See the <u>Intel Atom Processor E3800 Product Family Datasheet</u> of for a complete description of the CPU.

#### Note:

If the above link to the datasheet becomes inactive, search the internet for "Intel Bay Trail" or "E3800" and follow the results to the Intel site and datasheet.

### System RAM

The EPM-39 accepts one 204-pin SO-DIMM memory module (J9 connector on the bottom side of the board) with the following characteristics:

- Size Up to 8 GB, 1067 MHz CPU

- Voltage 1.35 V

- Type DDR3L (VersaLogic VL-MM9 Series modules)

### I/O Interfaces

The EPM-39 board's I/O interfaces and their associated connectors are described in later chapters as follows:

- Mass Storage Interfaces (SATA and mSATA)

- Multi-purpose I/O (USB, PCIe MiniCard and User I/O)

- Serial Ports

- Video Interfaces (Mini DisplayPort)

- Network Interfaces (Ethernet)

- Expansion Interfaces (PC/104)

### **Power Delivery**

#### **MAIN POWER CONNECTOR**

The figure below shows the location and pin orientation of the main power connector.

Figure 7. Location and Pin Orientation of the Main Power Connector

### **CAUTION:**

To prevent severe and possibly irreparable damage to the system, it is critical that the power connector is wired correctly. Make use of all +5 VDC pins and all ground pins to prevent excess voltage drop.

#### Note:

The +3.3 VDC, +12 VDC and -12 VDC inputs on the power connector are only required for PC/104-*Plus* and PC/104 expansion modules that require these voltages.

The following table lists the pinout for the main power connector.

**Table 3: J20 Main Power Connector Pinout**

| Pin | Signal   |

|-----|----------|

| 1   | Ground   |

| 3   | Ground   |

| 5   | Ground   |

| 7   | +3.3 VDC |

| 9   | Ground   |

| Pin | Signal  |

|-----|---------|

| 2   | +5 VDC  |

| 4   | +12 VDC |

| 6   | -12 VDC |

| 8   | +5 VDC  |

| 10  | +5 VDC  |

#### **CABLING**

An adapter cable, part number CBR-1008, is available for connecting the EPM-39 to an ATX power supply.

If your application requires a custom cable, the following information will be useful:

| EPM-39 Board Connector | Mating Connector |

|------------------------|------------------|

| FCI 78207-110HLF       | FCI 69176-010LF  |

#### **POWER DELIVERY CONSIDERATIONS**

Using the VersaLogic approved power supply (VL-PS200-ATX) and power cable (VL-CBR-1008) ensures high quality power delivery to the board. Customers who design their own power delivery methods should take into consideration the guidelines below to ensure good power connections.

In addition, the specifications for typical operating current do not include any off-board power usage that may be fed through the main power connector. Expansion boards and USB devices plugged into the board will source additional power through the main power connector.

- Do not use wire smaller than 22 AWG. Use high quality UL 1007 compliant stranded wire.

- The length of the wire should not exceed 18 inches.

- Avoid using any additional connectors in the power delivery system.

- The power and ground leads should be twisted together, or as close together as possible to reduce lead inductance.

- A separate conductor must be used for each of the power pins.

- All power input pins and all ground pins must be independently connected between the power source and the power connector.

- Use a high quality power supply that can supply a stable voltage while reacting to widely varying current draws.

#### **POWER BUTTON**

User I/O connector J4 includes an input for a push-button power switch. Shorting J4, pin 17 to ground causes the board to enter an S5 power state (similar to the Windows Shutdown state). Shorting it again returns the board to the S0 power state and reboots the board. The button can be configured in Windows to enter an S3 power state (Sleep, Standby, or Suspend-to-RAM), an S4 power state (Hibernate or Suspend-to-Disk), or an S5 power state (Shutdown or Soft-Off).

The input can be connected to ground using the normally open contacts of a pushbutton switch or a relay, or with a switching transistor (open-collector or open-drain) capable of sinking 3.3 mA with a voltage drop that is less than 500 mV (there is a 1 k $\Omega$  resistor on the EPM-39 pulled up to 3.3 V). Do not add an external pull-up resistor to this signal.

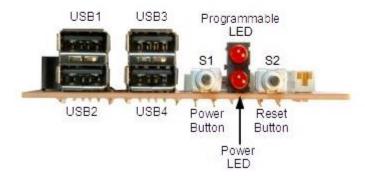

A power button is provided on the CBR-4005B paddleboard. See Figure 21 on page 41 for the location of the reset button on the CBR-4005B paddleboard.

In configurations where a power button is not connected to the board, if the system is put into an S5 state, power can be restored by turning off the power supply and turning it back on. This behavior is set by default in the BIOS.

#### **SUPPORTED POWER STATES**

The table below lists the board's supported power states.

**Table 4: Supported Power States**

| Power state | Description                                                                                                                                                                                                                                                                                                                                          |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S0 (G0)     | Working                                                                                                                                                                                                                                                                                                                                              |

| S1 (G1-S1)  | All processor caches are flushed, and the CPUs stop executing instructions. Power to the CPUs and RAM is maintained. Devices that do not indicate they must remain on may be powered down.                                                                                                                                                           |

| S3 (G1-S3)  | Commonly referred to as Standby, Sleep, or Suspend-to-RAM. RAM remains powered.                                                                                                                                                                                                                                                                      |

| S4 (G1-S4)  | Hibernation or Suspend-to-Disk. All content of main memory is saved to non-volatile memory, such as a hard drive, and is powered down.                                                                                                                                                                                                               |

| S5 (G2)     | Soft Off. Almost the same as G3 Mechanical Off, except that the power supply still provides power, at a minimum, to the power button to allow return to S0. A full reboot is required. No previous content is retained. Other components may remain powered so the computer can "wake" on input from the keyboard, clock, modem, LAN, or USB device. |

| G3          | Mechanical off (ATX supply switch turned off).                                                                                                                                                                                                                                                                                                       |

#### **BATTERY POWER OPTIONS**

The battery circuit on the EPM-39 provides power for the Real-Time Clock (RTC) and power to store BIOS Setup utility settings in non-volatile RAM.

The EPM-39 has multiple options for providing battery power:

- Use an external battery, connected to the board through the J8 external battery connector.

- Use the battery supplied with the CBR-4005B paddleboard

The figure below shows the location and pin orientation of the external battery connector.

Figure 8. Location and Pin Orientation of the External Battery Connector

#### **CABLING**

If your application requires a custom cable, the following information will be useful:

| EPM-39 Board Connector | Mating Connector  |  |

|------------------------|-------------------|--|

| Molex 501331-0207      | Molex 501330-0200 |  |

#### VL-CBR-0203 EXTERNAL BATTERY MODULE

The VL-CBR-0203 external battery module is compatible with the EPM-39. For more information, contact Sales@VersaLogic.com.

Figure 9. VL-CBR-0203 Latching Battery Module

### Real Time Clock (RTC)

The EPM-39 features a real-time clock/calendar (RTC) circuit. The RTC can be set using the BIOS Setup utility.

The EPM-39 supplies RTC voltage in S5, S3, and S0 states, but requires an external +2.75 V to +3.3 V the battery to maintain RTC functionality and RTC CMOS RAM when the board is not powered. The battery connection can be made to either (but not both) of the following:

- J8 external battery connector

- J4 user I/O connector

### **\( \sqrt{}** Integrator's Note:

There is no on-board battery. The EPM-39 board will operate without a battery, but to save the date and time, use a VL-CBR-4005B paddleboard (which includes a battery) or connect an external battery to connector J8.

### **Push-Button Reset**

User I/O connector J4 includes an input for a push-button reset switch. Shorting J4, pin 18 to ground causes the EPM-39 to reboot.

The input can be connected to ground using the normally open contacts of a pushbutton switch or a relay, or with a switching transistor (open-collector or open-drain) capable of sinking 3.3 mA with a voltage drop that is less than 500 mV (there is a 1 k $\Omega$  resistor on the EPM-39 pulled up to 3.3 V). Do not add an external pull-up resistor to this signal.

### 🛠 Integrator's Note:

The reset button has a switch de-bounce circuit in the FPGA that requires the button to be held asserted at least 125 ms (1/8 second) to reset the board. Holding the reset asserted on a Bay Trail processor does not continue to hold the processor in reset; it only resets on the edge of the assertion that follows the 125 ms de-bounce time interval).

A reset button is provided on the CBR-4005B paddleboard. See Figure 21 on page 41 for the location of the reset button on the CBR-4005B paddleboard.

### LEDs/Indicators

This figure shows the location of the boards LEDs/indicators.

Figure 10. Locations of the LEDs/Indicators

#### PROGRAMMABLE LED

User I/O connector J4 includes an output signal for attaching a software controlled LED. Connect the cathode of the LED to J4, pin 16; connect the anode to +3.3 V. An on-board 120  $\Omega$  resistor limits the current when the circuit is turned on. A programmable LED is provided on the CBR-4005B paddleboard. For instructions on how to switch the Programmable LED on and off, refer to the *EPM-39 Programmer's Reference Manual* (available on the <u>EPM-39 Product Page</u>).

#### **POWER LEDS**

The figure below shows the location of the dual green/yellow LED. This dual LED indicates the following:

The green LED illuminates when all power rails are within specified limits and indicates that the board is in the S0 power state. If any power rail is not within specified limits, the green LED will not illuminate. The green LED blinks at a slow rate when the processor is in a sleep or hibernate mode indicating that the sustain rail power is still within specified limits • The yellow LED is a fault indicator that illuminates if there is a problem with the processor booting. (Software can also be used to turn on this LED to indicate a major software failure.)

The power LED on the VL-CBR-4005B indicates that the paddleboard is being powered by the +3.3 V supply (though it does not indicate that all S0 power supplies are within specified limits). The LED is lit only when the board is in the S0 power state. If the board enters a Sleep or Hibernate mode, the LED will not be lit.

Figure 11. Location of the D11 Dual-color LED

## **External Speaker**

A miniature 8  $\Omega$  speaker can be connected between user I/O connector J4, pin 15 (SPKR#) and J4, pin 13 (V3P3). A speaker is provided on the CBR-4005B paddleboard.

## **Mass Storage Interfaces**

### **SATA**

The EPM-39 provides one 3 GB/s SATA port (J2). The SATA connector is a standard 7-pin right-angle connector with latching capability.

Power to the SATA drive is provided by the ATX power supply. Note that the standard SATA drive power connector is different from the typical 4-pin Molex connector used on IDE drives. Most current ATX power supplies provide SATA connectors, and many SATA drives provide both types of power connectors. If the power supply you are using does not provide SATA connectors, adapters are available.

Figure 12. Location of the SATA Port

## Multi-purpose I/O

### **USB** Interfaces

The EPM-39 includes four USB 2.0 host ports. The four USB 2.0 ports are incorporated into the J4 user I/O connector, with standard USB Type A connectors located on the VL-CBR-4005B paddleboard.

Figure 13. Location of the User I/O to VL-CBR-4005B

### PCIe Mini Card / mSATA

The socket at location J14 accepts a full-height PCI Express Mini Card or an mSATA module.

The PCIe Mini Card interface includes one PCIe x1 lane, one hubbed USB 2.0 channel, and the SMBus interface. The socket is compatible with plug-in Wi-Fi modems, GPS receivers, Flash data storage, and other cards for added flexibility. The VL-MPEs-F1E series of mSATA modules provide flash storage of 4 GB, 16 GB, or 32 GB.

For more information on PCIe Mini Cards offered by VersaLogic, contact <a href="Sales@VersaLogic.com">Sales@VersaLogic.com</a>.

To secure a Mini Card or mSATA module to the on-board standoffs, use two M2.5 x 6mm pan head Philips nylon screws. These screws are available in quantities of 10 in the VL-HDW-108 hardware kit from VersaLogic.

Table 5: PCle Mini Card / mSATA Pinout

| J14<br>Pin | PCIe Mini Card<br>Signal Name | PCIe Mini Card<br>Function |

|------------|-------------------------------|----------------------------|

| 1          | WAKE#                         | Wake                       |

| 2          | 3.3VAUX                       | 3.3V auxiliary source      |

| 3          | NC                            | Not connected              |

| 4          | GND                           | Ground                     |

| 5          | NC                            | Not connected              |

| 6          | 1.5V                          | 1.5V power                 |

| 7          | NC                            | Not connected              |

| 8          | NC                            | Not connected              |

| 9          | GND                           | Ground                     |

| 10         | NC                            | Not connected              |

| 11         | REFCLK-                       | Reference clock input –    |

| 12         | NC                            | Not connected              |

| 13         | REFCLK+                       | Reference clock input +    |

| 14         | NC                            | Not connected              |

| 15         | GND                           | Ground                     |

| 16         | NC                            | Not connected              |

| 17         | NC                            | Not connected              |

| 18         | GND                           | Ground                     |

| 19         | NC                            | Not connected              |

| 20         | W_DISABLE#                    | Wireless disable           |

| 21         | GND                           | Ground                     |

| 22         | PERST#                        | Card reset                 |

| 23         | PERn0                         | PCIe receive –             |

| 24         | 3.3VAUX                       | 3.3V auxiliary source      |

| 25         | PERp0                         | PCIe receive +             |

| 26         | GND                           | Ground                     |

| 27         | GND                           | Ground                     |

| 28         | 1.5V                          | 1.5V power                 |

| 29         | GND                           | Ground                     |

| 30         | SMB_CLK                       | SMBus clock                |

| 31         | PETn0                         | PCIe transmit –            |

| 32         | SMB_DATA                      | SMBus data                 |

| 33         | PETp0                         | PCIe transmit +            |

| 34         | GND                           | Ground                     |

| 35         | GND                           | Ground                     |

| 36         | USB_D-                        | USB data –                 |

| 37         | GND                           | Ground                     |

| 38         | USB_D+                        | USB data +                 |

| 39         | 3.3VAUX                       | 3.3V auxiliary source      |

| 40         | GND                           | Ground                     |

| 41         | 3.3VAUX                       | 3.3V auxiliary source      |

| 42         | LED_WWAN#                     | Wireless WAN LED           |

| 43         | GND                           | mSATA detect (Note 1)      |

| 44         | LED_WLAN#                     | Wireless LAN LED           |

| 45         | NC                            | Not connected              |

| mSATA<br>Signal Name | mSATA<br>Function             |

|----------------------|-------------------------------|

| Reserved             | Not connected                 |

| +3.3V                | 3.3V source                   |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| +1.5V                | 1.5V power                    |

| Reserved             | Not connected                 |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| +B                   | Host receiver diff. pair +    |

| +3.3V                | 3.3V source                   |

| -B                   | Host receiver diff. pair -    |

| GND                  | Ground                        |

| GND                  | Ground                        |

| +1.5V                | 1.5V power                    |

| GND                  | Ground                        |

| Two Wire I/F         | Two wire I/F clock            |

| -A                   | Host transmitter diff. pair - |

| Two Wire I/F         | Two wire I/F data             |

| +A                   | Host transmitter diff. pair + |

| GND                  | Ground                        |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| GND                  | Ground                        |

| Reserved             | Not connected                 |

| +3.3V                | 3.3V source                   |

| GND                  | Ground                        |

| +3.3V                | 3.3V source                   |

| Reserved             | Not connected                 |

| GND/NC               | Ground/not connected (Note 2) |

| Reserved             | Not connected                 |

| Vendor               | Not connected                 |

|            | _ |                               |                            |

|------------|---|-------------------------------|----------------------------|

| J14<br>Pin |   | PCIe Mini Card<br>Signal Name | PCIe Mini Card<br>Function |

| 46         |   | LED_WPAN#                     | Wireless PAN LED           |

| 47         |   | NC                            | Not connected              |

| 48         |   | 1.5V                          | 1.5V power                 |

| 49         |   | Reserved                      | Reserved                   |

| 50         |   | GND                           | Ground                     |

| 51         |   | Reserved                      | Reserved                   |

| 52         |   | 3.3VAUX                       | 3.3V auxiliary source      |

|            | - |                               |                            |

| mSATA<br>Signal Name | mSATA<br>Function        |

|----------------------|--------------------------|

| Reserved             | Not connected            |

| Vendor               | Not connected            |

| +1.5V                | 1.5V power               |

| DA/DSS               | Device activity (Note 3) |

| GND                  | Ground                   |

| GND                  | Ground (Note 4)          |

| +3.3V                | 3.3V source              |

#### Notes:

- 1. This pin is not grounded on the EPM-39 since it can be used to detect the presence of an mSATA module versus a PCIe Mini Card. Grounding this pin is available as an option on custom boards.

- 2. This pin is not grounded on the EPM-39 to make it available for mSATA module detection.

- This signal drives the blue LED activity indicator. This LED lights with mSATA disk activity, if supported by the mSATA module.

- 4. Some PCIe modules use this signal as a second Mini Card wireless disable input. On the EPM-39, this signal is available for use for mSATA versus PCIe Mini Card detection. There is an option in BIOS setup for setting the mSATA detection method.

#### **MSATA ACTIVITY LED**

The next figure shows the location (D12) of the SATA/mSATA activity blue LED. This LED indicates activity on either the SATA or the mSATA interface. Not all mSATA drives provide this disk activity signal.

Figure 14. Location of the SATA/mSATA Activity LED

#### **PCIE MINI CARD LEDS**

Two dual-colored PCIe Mini Card LEDs are provided on the EPM-39 at locations D9 and D8. This table lists the states of the LEDs. The next figure shows the location of the PCIe Mini Card LEDs.

**Table 6: PCle Mini Card LED States**

| LED | Color  | Status (when lit)                                                                                                                                                                 |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Green  | Activity on Wireless PAN (Note)                                                                                                                                                   |

| D9  |        | Illuminates when the 3.3 V power to the Mini Card is on. It alerts users to not hotplug the Mini Card. By default, Mini Card power stays on when the processor is in sleep modes. |

| Do  | Green  | Activity on Wireless WAN (Note)                                                                                                                                                   |

| D8  | Yellow | Activity on Wireless LAN (Note)                                                                                                                                                   |

**Note:** These LEDs will illuminate when the associated device is installed and capable of transmitting. Their function is determined by the installed device.

### **Integrator's Note:**

The 3.3 V power to the Mini Card can be controlled by the FPGA. By default, the power is always on, but there is a register setting that turns this power off in sleep modes. The Mini Card 1.5 V power is always turned off in sleep modes.

Figure 15. Location of PCIe Mini Card LEDs

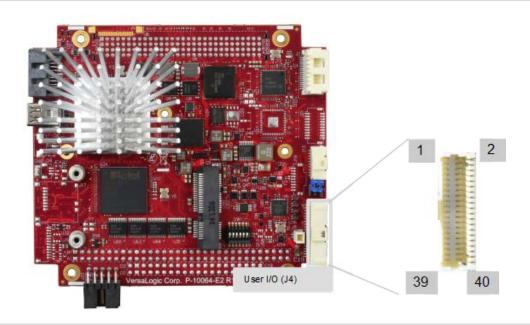

### **User I/O Connector**

The 40-pin J4 I/O connector incorporates the signals for the following:

- Four USB ports

- Eight GPIO lines. The eight GPIO lines on the paddleboard each have an alternate mode, accessible using the FPGA's AUXMOD1 register. Refer to the *EPM-39 Programmer's Reference Manual* for more information on FPGA registers.

- Two LEDs ( Ethernet link status LED and a programmable LED)

- Push-button power switch

- Push-button reset switch

- Speaker output

This connector uses IEC 61000-4-2-rated TVS components to help protect against ESD damage.

The next figure shows the location and pin orientation of the user I/O connector.

Figure 16. Location and Pin Orientation of User I/O Connector

This table provides the pinout of the user I/O connector.

Table 7: J4 I/O Connector Pinout and Pin Orientation

| Pin | Signal                   | Pin | Signal      |

|-----|--------------------------|-----|-------------|

| 1   | +5 V (V5_USB01)          | 2   | GND         |

| 3   | USB0_P                   | 4   | USB1_P      |

| 5   | USB0_N                   | 6   | USB1_N      |

| 7   | +5V (V5_USB23)           | 8   | GND         |

| 9   | USB2_P                   | 10  | USB3_P      |

| 11  | USB2_N                   | 12  | USB3_N      |

| 13  | +3.3 V (Note 1)          | 14  | GND         |

| 15  | SPKR#                    | 16  | PLED#       |

| 17  | PWR_BTN#                 | 18  | RST_BTN#    |

| 19  | GND                      | 20  | GND         |

| 21  | I2C Clock                | 22  | V_BATT      |

| 23  | I2C Data                 | 24  | RETURN_BATT |

| 25  | GND                      | 26  | GND         |

| 27  | FPGA GPIO1               | 28  | FPGA GPIO2  |

| 29  | FPGA GPIO3               | 30  | FPGA GPIO4  |

| 31  | GND                      | 32  | GND         |

| 33  | FPGA GPIO5               | 34  | FPGA GPIO6  |

| 35  | FPGA GPIO7               | 36  | FPGA GPIO8  |

| 37  | +3.3 V ( <b>Note 2</b> ) | 38  | GND         |

| 39  | ETH0 LED                 | 40  | Reserved    |

#### Notes:

#### **CABLING**

An adapter cable, part number CBR-4005 is available for connecting the CBR-4005B paddleboard to the EPM-39. This is a 12-inch, Pico-Clasp 40-pin to 40-pin cable

If your application requires a custom cable, the following information will be useful:

| EPM-39 Board Connector | Mating Connector  |  |

|------------------------|-------------------|--|

| Molex 501571-4007      | Molex 501189-4010 |  |

<sup>1.</sup> This 3.3 V power goes off in sleep modes. The SPKR# uses this power as should the PLED# (there is no requirement for PLED# to use this power, but the CBR-4005 paddleboard does).

<sup>2.</sup> This 3.3 V power can be turned on our off similar to the 3.3V power to the Mini Card via the FPGA (can go off in sleep modes or always stay on; by default it goes off in sleep modes). It is used for the 10 k $\Omega$  pullup resistor power on the 8x GPIOs and usually for the 2x Ethernet LEDs, however, the Ethernet LEDs can be powered by a 3.3 V power source.

# **Serial Ports**

The EPM-39 features two on-board 16550-based serial communications channels located at standard PC I/O addresses. The serial ports can be operated in RS-232 4-wire, RS-422, or RS-485 modes. IRQ lines are chosen in the BIOS Setup utility. Each COM port can be independently enabled, disabled, or assigned a different I/O base address in the BIOS setup utility.

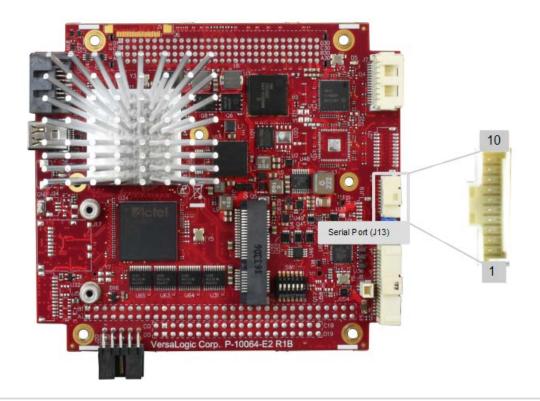

# **Serial Port Connectors**

The next figure shows the location and pin orientation of the serial port connector.

Figure 17. Location and Pin Orientation of Serial Port Connector

## **SERIAL PORT CONNECTOR PINOUTS**

Table 8: J13 COM1/COM2 Connector Pinout

| Pin | RS-232 Signal | RS-422/RS-485 Signal | Port   |

|-----|---------------|----------------------|--------|

| 1   | RTS1          | TXD1_P               |        |

| 2   | TXD1#         | TXD1_N               | COM1   |

| 3   | CTS1          | RXD1_P               | COIVIT |

| 4   | RXD1#         | RXD1_N               |        |

| 5   | GND           | GND                  | _      |

| 6   | RTS2          | TXD2_P               |        |

| 7   | TXD2#         | TXD2_N               | COM2   |

| 8   | CTS2          | RXD2_P               | COIVIZ |

| 9   | RXD2#         | RXD2_N               |        |

| 10  | GND           | GND                  | _      |

# **CABLING**

An adapter cable, part number CBR-1014, is available for routing the J13 signals to 9-pin D-sub connectors. This is a 12-inch, Pico-Clasp 10-pin to two 9-pin D-sub connector cable.

If your application requires a custom cable, the following information will be useful:

| EPM-39 Board Connector | Mating Connector  |

|------------------------|-------------------|

| Molex 501331-1007      | Molex 501330-1000 |

# **RS-485 Mode Line Driver Control**

The transmit line driver can be automatically turned on and off based on data availability in the UART output FIFO. This mode can be enabled in the BIOS setup utility. The transmit line driver can be enabled in the BIOS Setup utility.

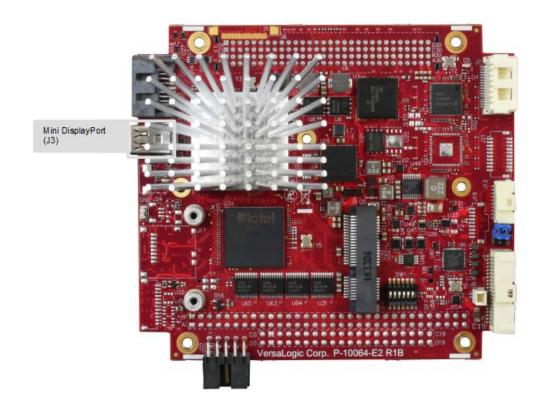

Video Interfaces

The EPM-39 incorporates the Intel Gen-7 graphics core with four Execution Units and Turbo Boost. It supports two independent displays. It also supported formats including DirectX 11, OpenGL 3, VP8, MPEG2, H.264, VC1, 2 HD streams (1080p@30fps), Flash and WMP support.

The analog (VGA) and Mini DisplayPort video interfaces support Extended Desktop, Clone, and Twin display modes.

The optional VL-EPH-V6 video adapter card converts DisplayPort output to LVDS for flat panel operation.

# **Mini DisplayPort Connector**

DisplayPort consists of three interfaces:

- Main Link transfers high-speed isochronous video and audio data

- Auxiliary channel used for link management and device control; the EDID is read over this interface

- Hot Plug Detect indicates that a cable is plugged in

The DisplayPort interface supports:

- Audio signaling

- DP++ mode allowing connection to an HDMI device through a passive adapter.

"Passive" means that the adapter does not require external power (because it uses the DP port's 3.3 V power) and it does not require software drivers.

The next figure shows the location of the 20-pin Mini DisplayPort connector. Table 9 lists the pinout of the J3 Mini DisplayPort connector.

Figure 18. Location of the Mini DisplayPort Connector

Table 9: J3 Mini DisplayPort Connector Pinout

| Pin | Signal     |

|-----|------------|

| 1   | GND        |

| 3   | ML_LANE0_P |

| 5   | ML_LANE0_N |

| 7   | GND        |

| 9   | ML_LANE1_P |

| 11  | ML_LANE1_N |

| 13  | GND        |

| 15  | ML_LANE2_P |

| 17  | ML_LANE2_N |

| 19  | RTN        |

| Pin | Signal          |

|-----|-----------------|

| 2   | HOT PLUG DETECT |

| 4   | CONFIG 1        |

| 6   | CONFIG 2        |

| 8   | GND             |

| 10  | ML_LANE3_P      |

| 12  | ML_LANE3_N      |

| 14  | GND             |

| 16  | AUX_CH_P        |

| 18  | AUX_CH_N        |

| 20  | DP_POWER        |

# **Console Redirection**

The EPM-39 can be configured for remote access by redirecting the console to a serial communications port. The BIOS setup utility and some operating systems (such as MS-DOS) can use this console for user interaction. The default settings for the redirected console are as follows:

- 115,200 baud rate

- 8 data bits, no parity

- 1 stop bit)

- No parity

- No flow control

# **Network Interfaces**

The EPM-39 provides a single on-board Intel I210-IT Gigabit Ethernet controller. The controller provides a standard Ethernet interface for 1000Base-T, 100Base-TX, and 10Base-T applications. The I210-IT Ethernet controller auto-negotiates connection speed. Drivers are available to support a variety of operating systems.

### **ETHERNET CONNECTOR**

The J7 connector provides access to the Ethernet port 0. The J7 connector uses IEC 61000-4-2-rated TVS components to help protect against ESD damage. The figure below shows the location and pin orientation of the Ethernet connector.

Figure 19. Location and Pin Orientation for the J7 Ethernet Connector

The table below lists the pinout of the Ethernet connector.

**Table 10: Ethernet Connector Pinout**

|       |     |                          | _                      |   |     |           |

|-------|-----|--------------------------|------------------------|---|-----|-----------|

|       | Pin | 10/100 Signals           | 10/100/1000<br>Signals |   | Pin | 10/10     |

|       | 1   | - Auto Switch (Tx or Rx) | BI_DD-                 | Ī | 2   | + Auto Sv |

| ort 0 | 3   | - Auto Switch (Tx or Rx) | BI_DB-                 | Ī | 4   | + Auto Sv |

| Pol   | 5   | - Auto Switch (Tx or Rx) | BI_DC-                 | Ī | 6   | + Auto Sv |

|       | 7   | - Auto Switch (Tx or Rx) | BI DA-                 | Ī | 8   | + Auto Sv |

| Pin | 10/100 Signals           | 10/100/1000<br>Signals |     |

|-----|--------------------------|------------------------|-----|

| 2   | + Auto Switch (Tx or Rx) | BI_DD+                 |     |

| 4   | + Auto Switch (Tx or Rx) | BI_DB+                 | 1.0 |

| 6   | + Auto Switch (Tx or Rx) | BI_DB+                 | Pol |

| 8   | + Auto Switch (Tx or Rx) | BI_DA+                 |     |

### **CABLING**

An adapter cable, part number CBR-1605, is available. This is a 12-inch, 8-pin Click-Mate to a RJ-45 connector cable.

If your application requires a custom cable, the following information will be useful:

| EPM-39 Board Connector | Mating Connector  |

|------------------------|-------------------|

| Molex 503148-1690      | Molex 503149-1600 |

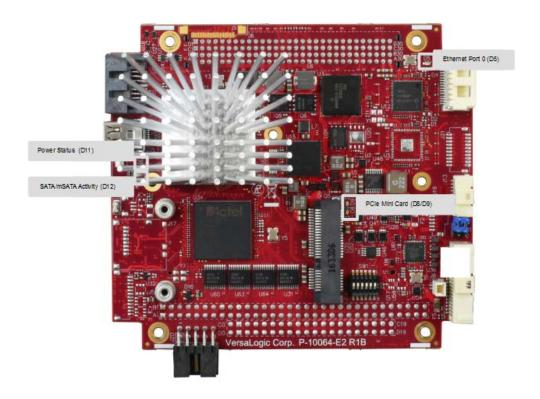

## **ON-BOARD ETHERNET STATUS LEDS**

On-board status LEDs are provided for the Ethernet port:

D5 (green LED) provides status for Ethernet port 0

Figure 20. Location of Ethernet Status LED

**Table 11: Ethernet Status LEDs**

| Ethernet Port | LED | State | Description                            |

|---------------|-----|-------|----------------------------------------|

| Dort O        | Dr  | On    | Cable connected (blinks with activity) |

| Port 0 D5     |     | Off   | Cable not connected                    |

# PC/104-Plus Expansion Bus

The EPM-39 provides a legacy stack-down PCI connector at locations J11 (for PCI) and J10 (for ISA) on the bottom side of the board for PC/104-*Plus* (PCI +ISA) as well as PCI-104 (PCI only) and PC/104 (ISA only) expansion modules. Figure 3 on page 3 shows the locations of these connectors.

# **Integrator's Notes:**

- PC/104 ISA only modules (those that have no PCI connector) must not be positioned below the PC/104-Plus (PCI+ISA) modules in the stack.

- Modules with PCI interfaces must be above those with only ISA interfaces.

- PCI-104 PCI only modules (those with no ISA connector) must not be positioned below the PC/104-Plus (PCI+ISA) modules in the stack.

- In general, PC/104 (ISA only) and PCI-104 (PCI only) cards can never be used together in a stack.

The table below lists the maximum PC/104-*Plus* slot current rating on the EPM-39. This is the aggregate power available to both the PCI and ISA connectors. ISA does not use +3.3 V power, so all of the +3.3 V power is available for the PCI connector.

Table 12: PCI/104-Plus Connector (PCI) Maximum Current

| Voltage | Maximum Current |

|---------|-----------------|

| +5 V    | 4.0 A           |

| +3.3 V  | 3.0 A           |

| +12 V   | 1.0 A           |

| -12 V   | 0.5 A           |

# ISA Bus (on PC/104-PLUS AND PC/104 EXPANSION MODULES)

Refer to the ISA sections of the <u>PC/104-Plus Specification</u> for a complete description of this interface.

The EPM-39 implements the ISA bus on PC/104-*Plus* and PC/104 expansion modules using an LPC-to-ISA bridge implemented in the FPGA. This LPC-to-ISA bridge supports all features except the following:

- The ISA bus must not be mastered by an external module. The EPM-39 is always the bus master. The MASTER signal on pin D17 of J10 is not connected.

- The REFRESH output signal on B19 of J10 is not supported; it is pulled up to a high logic level.

- DMA is not supported. The seven DACKx outputs on pins B15, B17, B26, D8, D10, D12, and D14 on J10 are pulled up to a high logic level. The seven DRQx inputs on pins B6, B16, B18, D9, D11, D13, and D15 on J10 are not connected. The Terminal Count (TC) output on pin B27 of J10 is pulled low.

- -5.0V power is not provided on J10 pin B5. This pin is not connected.

Most PC/104-*Plus* (PCI +ISA) or PC/104 (ISA only) expansion modules will work, but be sure to check the requirements of your PC/104 card against the list above.

### **ISA I/O SUPPORT**

Both 8-bit and 16-bit I/O cycles are supported, but for 16-bit cycles the PC/104 (ISA) module must be 16-bit capable and must assert IOCS16#.

The next table lists the I/O ranges available on the ISA bus unless there is a device claiming the range on the LPC or PCI bus. The FPGA on the EPM-39 uses I/O addresses 0xC80-0xCBF and, if enabled, the FPGA has two COM ports that can be configured in the BIOS Setup utility to map to various address ranges.

By default, the two COM ports in the FPGA are enabled and occupy the I/O address ranges of 0x3F8-0x3FF and 0x2F8-0x2FF. The following are the I/O address ranges available on the ISA bus when the BIOS is configured to factory defaults.

Table 13: Available ISA Bus I/O Ranges

| ■ 0x0 − 0x1F  | ■ 0x3E – 0x3F | ■ 0x93 – 0x9F  | ■ 0x300 – 0x3AF |

|---------------|---------------|----------------|-----------------|

| ■ 0x22 - 0x23 | ■ 0x43 – 0x4F | ■ 0xA2 – 0xA3  | ■ 0x3BC – 0x3BF |

| ■ 0x26 - 0x27 | ■ 0x53 – 0x5F | ■ 0xA6 – 0xA7  | ■ 0x3E0 – 0x3F7 |

| ■ 0x2A – 0x2B | ■ 0x62        | ■ 0xAA – 0xAB  | ■ 0x480 – 0x4CF |

| ■ 0x2E – 0x2F | ■ 0x66        | ■ 0xAE – 0xAF  | ■ 0x4D2 – 0x4FF |

| ■ 0x32 - 0x33 | ■ 0x68 – 0x70 | ■ 0xB6 – 0xB7  | ■ 0x600 – 0xC7F |

| ■ 0x36 - 0x37 | ■ 0x78 – 0x7F | ■ 0xBA – 0xBB  | ■ 0xCC0 – 0xCF8 |

| ■ 0x3A – 0x3B | ■ 0x90 – 0x91 | ■ 0xBE – 0x2F7 | ■ 0xCFA – 0xCFB |

Assuming the COM ports in the FPGA are disabled, the available I/O base addresses for COM ports on the ISA bus are as follows:

0x200

0x228

0x338

0x208

0x238

0x3E8

0x220

0x2E8

0x3F8

Each COM port in the FPGA that is enabled will use one of these I/O base addresses and, in that case, that 8 byte I/O range will not be available on the ISA bus. PCI devices may be assigned I/O space, but that usually occurs at I/O address 0x1000 or higher so as to not conflict with legacy I/O devices.

## **ISA MEMORY SUPPORT**

The following memory addresses are available on the ISA bus:

■ 0xA0000 - 0xB7FFF

## **ISA IRQ SUPPORT**

The following IRQs are supported on the ISA bus:

- IRQ3

IRQ9

- IRQ4

IRQ10

- IRQ5

IRQ11

- IRQ6

IRQ12

- IRQ7

IRQ15

Each of the IRQs must be enabled in the BIOS Setup utility before they can be used. (All are disabled by default.)

Because ISA IRQ sharing is not supported, IRQs may not be available to the ISA bus due to operating system limitations.

# PCI Bus (on PC/104-PLUS AND PCI-104 EXPANSION MODULES)

Refer to the PCI sections of the <u>PC/104-Plus Specification</u> for a complete description of this interface.

Make sure to correctly configure the PCI slot position jumpers on each PC/104-*Plus* or PCI-104 module appropriately.

The BIOS automatically allocates I/O, memory, and interrupt resources.

# System Resources and Maps

10

Refer to the *EPM-39 Programmer's Reference Manual* for the following information:

- Memory map

- IRQ map

- I/O map

- FPGA register map

- FPGA register descriptions

- Programming information for certain hardware interfaces.

# **CBR-4005B Paddleboard**

# **CBR-4005B Paddleboard**

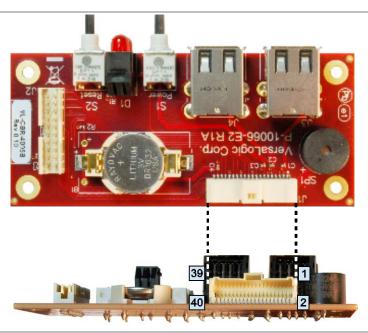

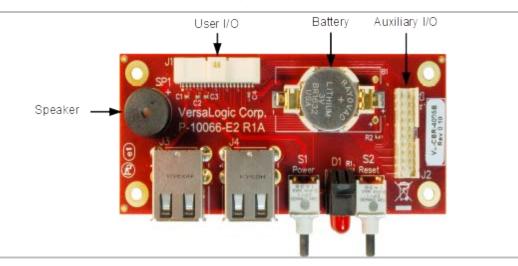

# **CBR-4005B CONNECTORS AND INDICATORS**

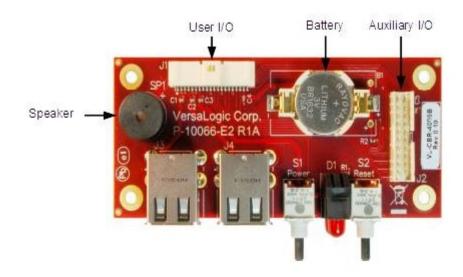

The figure below shows the locations of the connectors, switches, and LEDs on the CBR-4005B paddleboard.

Figure 21. CBR-4005B Connectors, Switches, and LEDs

# **USER I/O CONNECTOR**

The next figure shows the location and pin orientation of the user I/O connector.

Figure 22. Location and Pin Orientation of the User I/O Connector

Table 14: User I/O Connector Pinout

| Pin | Signal     |

|-----|------------|

| 1   | +5 V       |

| 3   | USB1_P     |

| 5   | USB1_N     |

| 7   | +5V        |

| 9   | USB3_P     |

| 11  | USB3_N     |

| 13  | +3.3 V     |

| 15  | SPKR#      |

| 17  | PWR_BTN#   |

| 19  | GND        |

| 21  | Reserved   |

| 23  | Reserved   |

| 25  | GND        |

| 27  | FPGA GPIO1 |

| 29  | FPGA GPIO3 |

| 31  | GND        |

| 33  | FPGA GPIO5 |

| 35  | FPGA GPIO7 |

| 37  | +3.3 V     |

| 39  | ETH0 LED   |

| Pin | Signal        |

|-----|---------------|

| 2   | GND           |

| 4   | USB2_P        |

| 6   | USB2_N        |

| 8   | GND           |

| 10  | USB4_P        |

| 12  | USB4_N        |

| 14  | GND           |

| 16  | PLED#         |

| 18  | RST_BTN#      |

| 20  | GND           |

| 22  | V_BATT        |

| 24  | V_BATT_RETURN |

| 26  | GND           |

| 28  | FPGA GPIO2    |

| 30  | FPGA GPIO4    |

| 32  | GND           |

| 34  | FPGA GPIO6    |

| 36  | FPGA GPIO8    |

| 38  | GND           |

| 40  | Reserved      |

### **CABLING**

An adapter cable, part number CBR-4005, is available for connecting the CBR-4005B paddleboard to the EPM-39. This is a 12-inch, Pico-Clasp 40-pin to 40-pin cable

If your application requires a custom cable, the following information will be useful:

| CBR-4005B Board Connector | Mating Connector  |

|---------------------------|-------------------|

| Molex 501571-4007         | Molex 501189-4010 |

## **ON-BOARD BATTERY**

# **CAUTION:**

To prevent shorting, premature failure or damage to the Lithium battery, do not place the board on a conductive surface such as metal, black conductive foam or the outside surface of a metalized ESD protective pouch. The Lithium battery may explode if mistreated. Do not recharge, disassemble, or dispose of the battery in fire. Dispose of used batteries promptly.

Nominal battery voltage is 3.0 V. If the voltage drops below 2.7 V, contact the factory for a replacement. The life expectancy under normal use is approximately five years.

# **AUXILIARY I/O CONNECTOR**

The figure below shows the location and pin orientation of the auxiliary I/O connector.

Figure 23. Location and Pin Orientation of Auxiliary I/O Connector

Table 15: Auxiliary I/O Connector Pinout

| Pin | Signal              |

|-----|---------------------|

| 1   | Reserved            |

| 3   | Reserved            |

| 5   | GND                 |

| 7   | FPGA GPIO1          |

| 9   | FPGA GPIO3          |

| 11  | GND                 |

| 13  | FPGA GPIO5          |

| 15  | FPGA GPIO7          |

| 17  | +3.3 V              |

| 19  | Ethernet Port 0 LED |

| Pin | Signal        |

|-----|---------------|

| 2   | V_BATT        |

| 4   | V_BATT_RETURN |

| 6   | GND           |

| 8   | FPGA GPIO2    |

| 10  | FPGA GPIO4    |

| 12  | GND           |

| 14  | FPGA GPIO6    |

| 16  | FPGA GPIO8    |

| 18  | GND           |

| 20  | Reserved      |

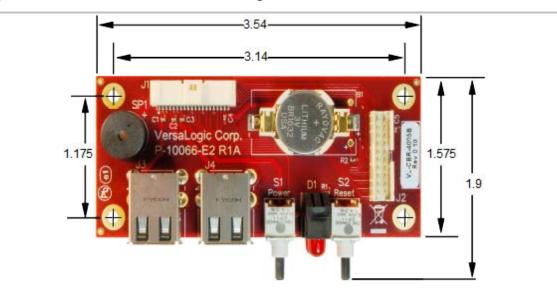

# **DIMENSIONS AND MOUNTING HOLES**

Figure 24. CBR-4005B Dimensions and Mounting Holes

# **Thermal Considerations**

This chapter discusses the following topics related to thermal configuration:

■ EPM-39 thermal characterization

# The Thermal Solution for Your Application

This section provides guidelines for the overall system thermal engineering effort.

### **HEAT SINK**

The heat sink supplied with the EPM-39 is the basis of the thermal solution. The heat sink draws heat away from the CPU chip as well as other critical components such as the power supply / management unit, the PCIe-to-PCI Bridge, and the Ethernet interfaces. Other components rely on the ambient air temperature being maintained at or below the maximum specified 85 °C.

# **CAUTION:**

The heat sink is permanently affixed to the EPM-39 and must not be removed. Removal of the heat plate voids the product warranty. Attempting to operate the EPM-39 without the heat sink voids the product warranty and can damage the CPU.

#### **GENERAL SYSTEM-LEVEL CONSIDERATIONS**

The EPM-39 thermal solution is part of the larger thermal system of the application. Other PC/104 boards stacked under the EPM-39 and any other nearby heat sources (power supplies or other circuits), all contribute to how the EPM-39 will perform from a thermal standpoint.

The ambient air surrounding the EPM-39 needs to be maintained at 85 °C or below. This can prove to be challenging depending on how and where the EPM-39 is mounted in the end user system. Standard methods for addressing this requirement include the following:

- Provide a typical airflow of 100 linear feet per minute (LFM) / 0.5 linear meters per second (as described in the section titled EPM-39 Thermal Characterization) within the enclosure

- Position the EPM-39 board to allow for convective airflow

- Lower the system level temperature requirement as needed

The decision as to which thermal solution to use can be based on several factors including (but not limited to) the following:

- Number of CPU cores in the SoC (single, dual, or quad)

- CPU core program utilization

- Temperature range within which the EPM-39 will be operated

- Air movement (or lack of air movement)

- Video processing intensity

- Memory access demands

- High speed I/O usage (PCIe, USB and SATA usage)

Most of these factors involve the demands of the user application on the EPM-39 and cannot be isolated from the overall thermal performance. Due to the interaction of the user application, the EPM-39 thermal solution, and the overall environment of the end system, thermal performance cannot be rigidly defined.

#### **CPU THERMAL TRIP POINTS**

The CPU cores in the EPM-39 have their own thermal sensors. Coupled with these sensors are specific reactions to four thermal trip points. The next table describes the four thermal trip points.

**Table 16: CPU Thermal Trip Points**